intersil

# 200W, 470kHz, Telecom Power Supply Using ISL6551 Full-Bridge Controller and ISL6550 Supervisor and Monitor

**Application Note**

August 2002

AN1002

Author: Chun Cheung

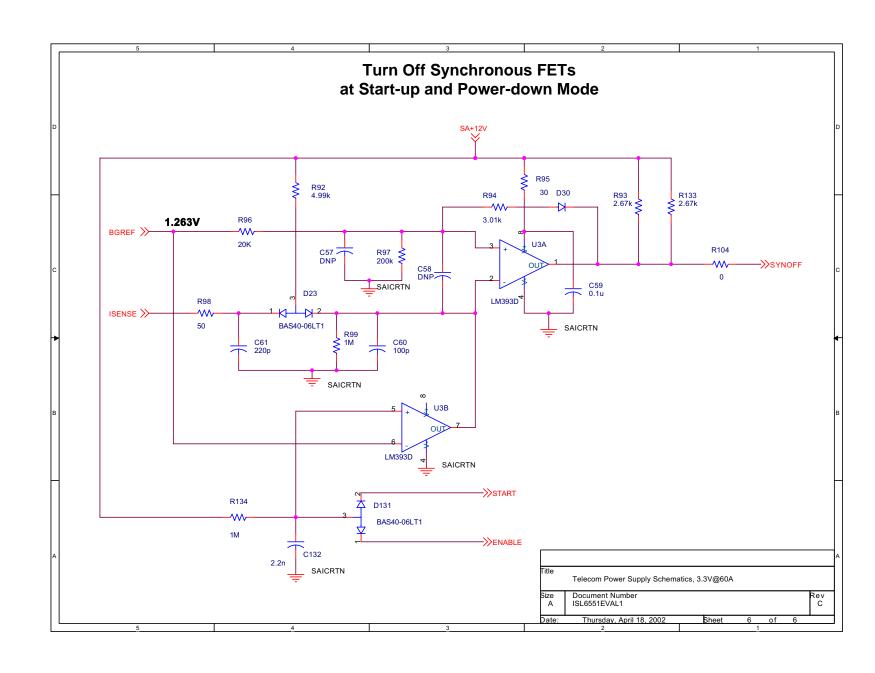

# Abstract

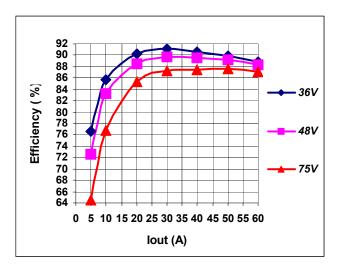

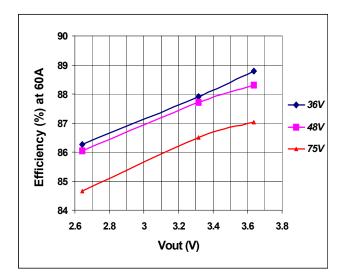

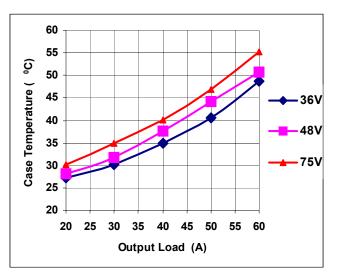

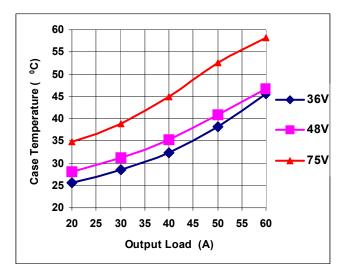

This application note highlights design considerations for a 200W, 470kHz, telecom power supply using Intersil's ISL6551 ZVS Full-Bridge Controller and ISL6550 Supervisor And Monitor. The zero-voltage switching technique of the ISL6551 is presented in detail. A step-by-step design procedure for a 48V-to-3.3V@60A with 88% efficiency converter based on these two chips, incorporating both ZVS full bridge and current doubler topologies, is described. A few tips for design and debugging are then listed. Finally, experimental results with discussion gives users a deeper understanding of the performance of the reference design and the advantages of the ISL6550 and ISL6551.

# Introduction

In medium to high power applications with extreme efficiency requirements, the full-bridge topology is probably the best choice. Besides great transformer utilization with this topology, higher efficiency and lower EMI levels are the major benefits if utilizing circuit parasitics, which include output capacitance of the bridge FETs, primary capacitance of the transformer, and leakage inductance, to achieve zerovoltage transitions (ZVT). In the conventional full bridge converter, these advantages cannot be realized without employing a significant amount of soft-switching/resonant circuitry which adds cost and circuit board real estate. Intersil's ISL6551 full-bridge controller implements a unique control algorithm, rather than the traditional phase-shifted control technique introduced by TI's UC3875, to achieve ZVS with few components. In addition, the ISL6551 integrates additional sophisticated features such as Leading Edge Blanking, Latching Shutdown Input, Enable Input, Current Share Support, Fast Short-Circuit Shutdown, Synchronous Drive Signals, and Power Good Indication that the UC3875 does not provide. The ISL6551 enables a complete and sophisticated power supply solution and can save board space and engineering effort as well as cost.

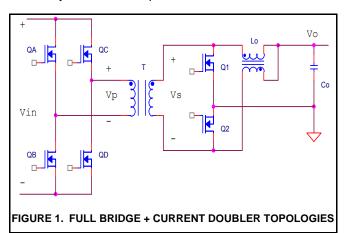

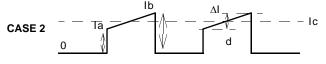

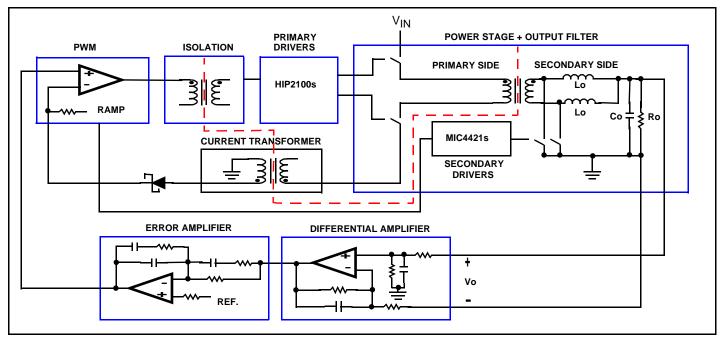

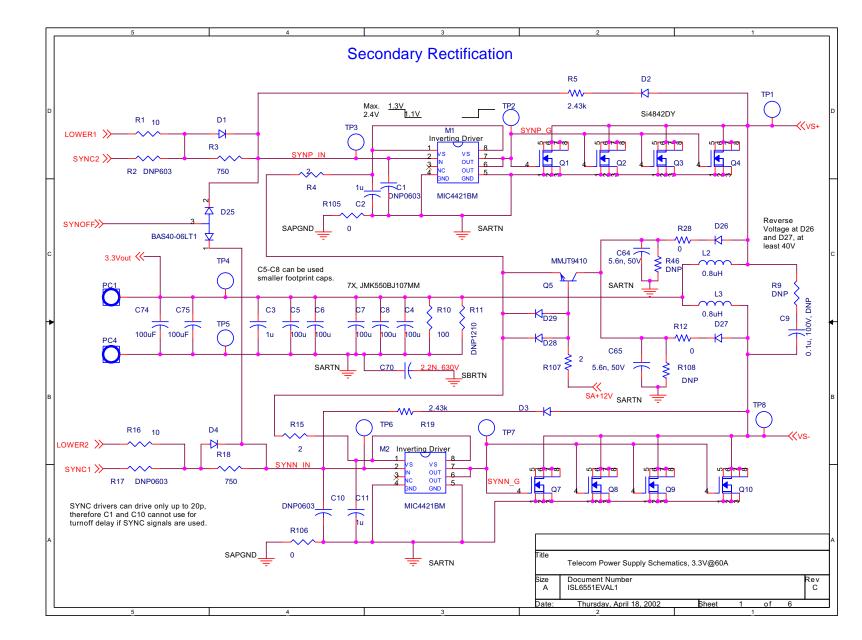

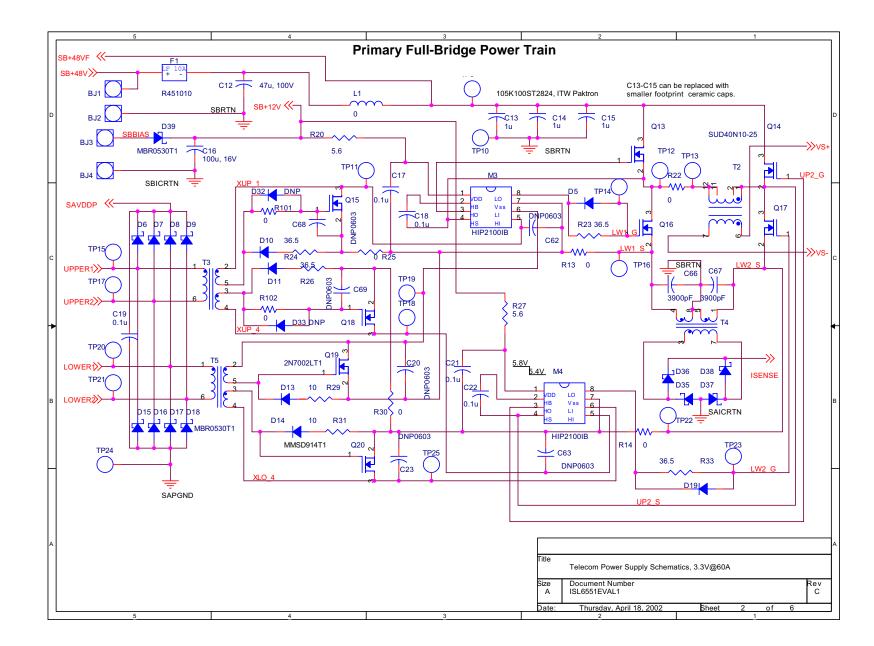

This application note provides detailed design considerations of a 200W telecom power supply reference design employing both Intersil's ISL6551 full-bridge controller and ISL6550 Supervisor and Monitor while taking advantage of both ZVS full-bridge and current doubler topologies, as shown in Figure 1.

An alternative secondary rectification technique for push-pull and bridge converters is introduced by Laszlo Balogh in his paper [2]. This technique offers potential benefits of better distributed power dissipation in densely packed power supplies and in medium to high power and/or high output current applications [2].

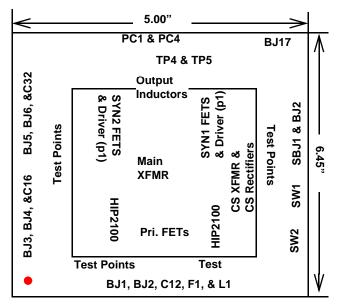

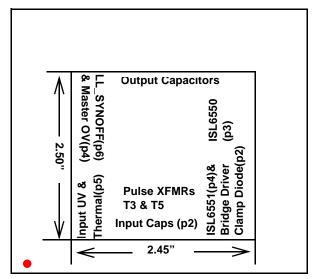

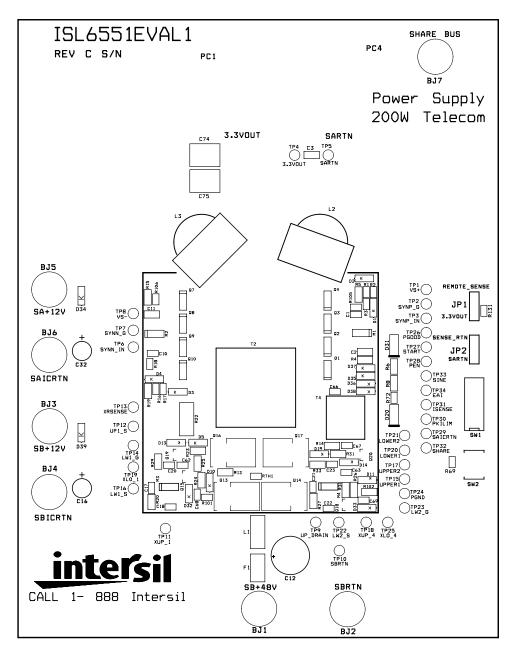

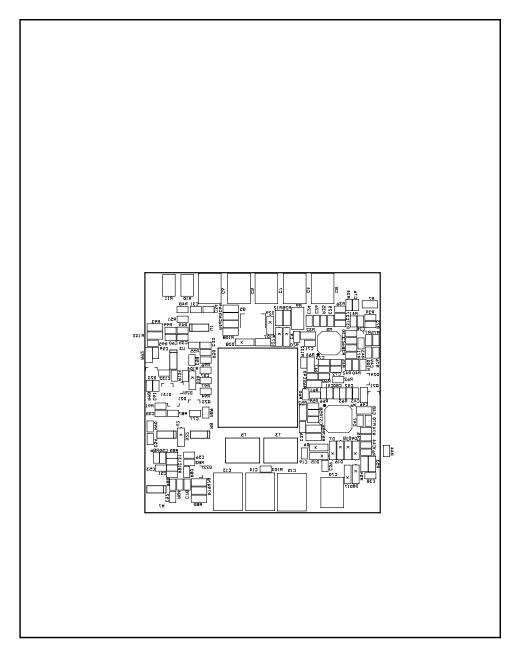

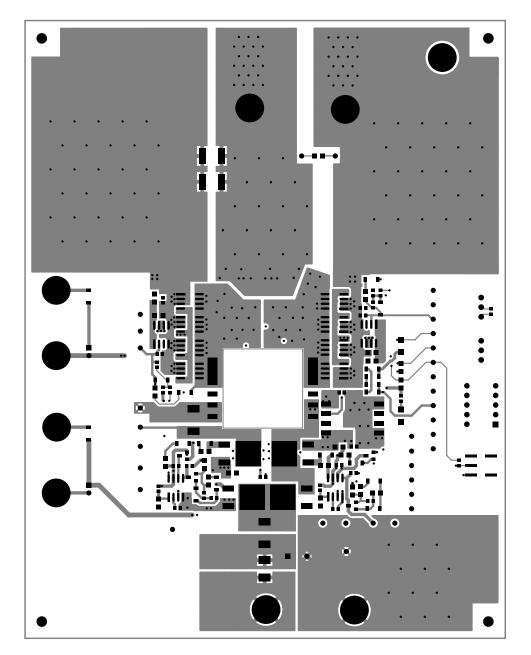

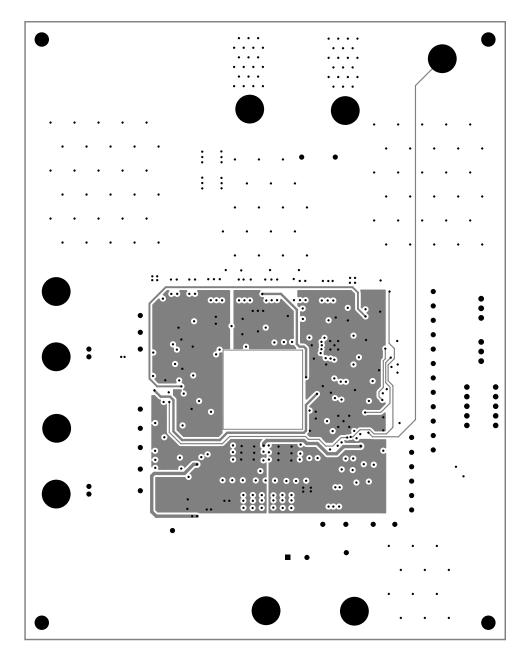

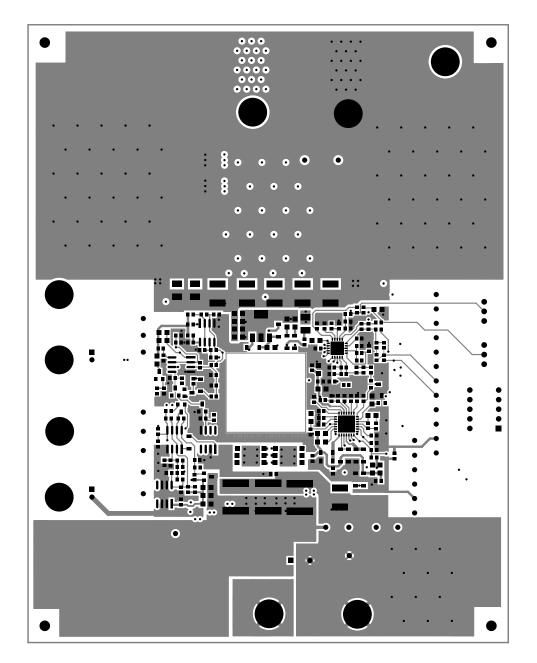

This converter is designed to meet the specification of an industry-standard half brick. Most of the converter circuits are placed in the central 2.50"x2.45" area and limited within 0.5" height, and all other unnecessary components such as test point connectors and I/O connectors are placed beyond this area. To easily modify the evaluation board for a broader base of applications, additional circuits are designed in and

magnetics components are not integrated with the PCB. This expands the area of the evaluation board when compared to a standard half-brick design. This DC/DC converter accepts a wide range input of 36V to 75V and generates a DAC-adjustable wide range output of 2.64V to 3.63V with 31.918mV step. An ultra high efficiency of 88% at 3.312V with a fully loaded 60A output has been achieved.

This application note first introduces the unique ZVS technique of the ISL6551. The Supervisor and Monitor ISL6550 chip is then briefly introduced. Thereafter, a stepby-step design procedure for the reference design is followed, including power train component selection, component power dissipation calculations, magnetics design parameter calculations, and control loop design. A few tips for design and debugging are listed. Finally, experimental results of the evaluation board are discussed. Term Definitions, Block Diagram, Schematics, Layout, Bill of Materials, References, and Preliminary Specifications of the Reference Design are included at the end of this paper.

# Intersil ZVS Full Bridge Controller: ISL6551

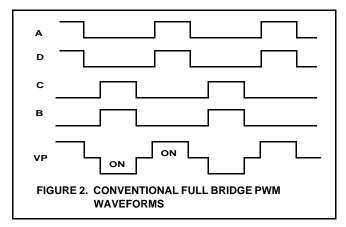

The diagonal bridge switches are turned on together in a conventional full bridge converter which alternatively places the input voltage,  $V_{IN}$ , across the primary of the transformer for a period of Ton, as shown in Figure 2. The limiting factor of achieving optimum efficiency in this circuit is the hard switching nature of the operation, which causes significant

switching losses in high frequency, high input voltage, and /or high current applications. The switching losses can be reduced by employing snubbers, or quasi- or fully resonant, soft-switching circuits [1].

In the ISL6551, rather than driving both of the diagonal full bridge switches together, the two upper switches (QA & QC)

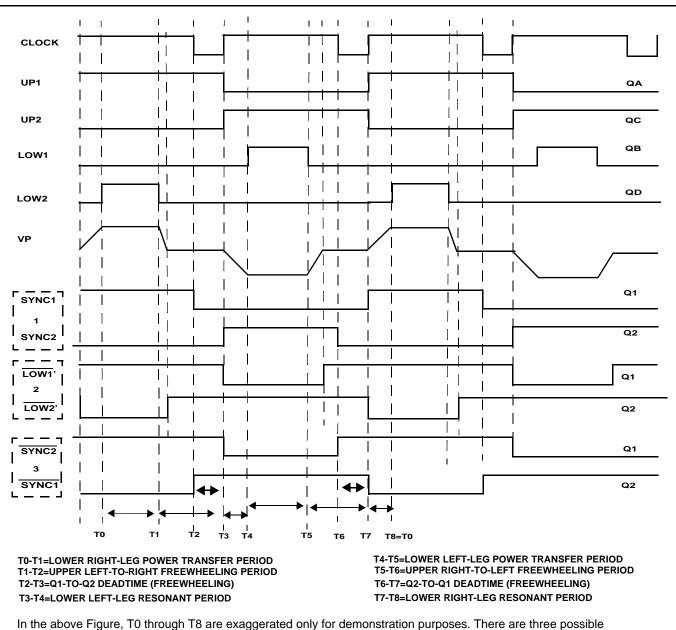

are driven at a fixed 50% duty cycle and the two lower switches (QB & QD) are PWM-controlled on the trailing edge while the leading edge employs resonant delay. Figure 4 shows the drive signals of four bridge FETs and three options for synchronous rectification. The basic control principle of the ISL6551 is different from that of the UC3875's phase-shift control which varies the phase between two 50% duty cycle control signals [1], requiring additional circuitry to derive the synchronous control signals and therefore adding cost.

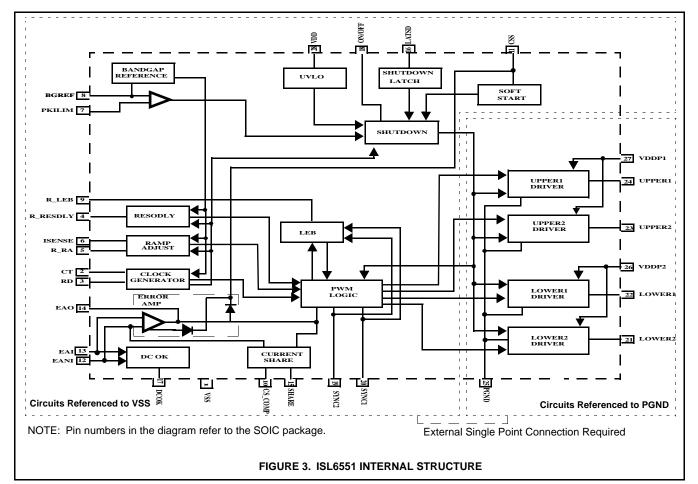

The ISL6551 is a ZVS full bridge controller that Intersil has designed for medium to high power AC/DC and DC/DC applications with ultra high efficiency requirements. The ISL6551 includes many integrated features for a more complete and sophisticated telecom or off-line power supply solution. The internal architecture of the IC is shown in Figure 4. Detailed ZVS operation of the ISL6551 will be presented by describing switching actions of the power train at each time interval in the following sections. Refer to the device datasheet for the operation of the integrated features.

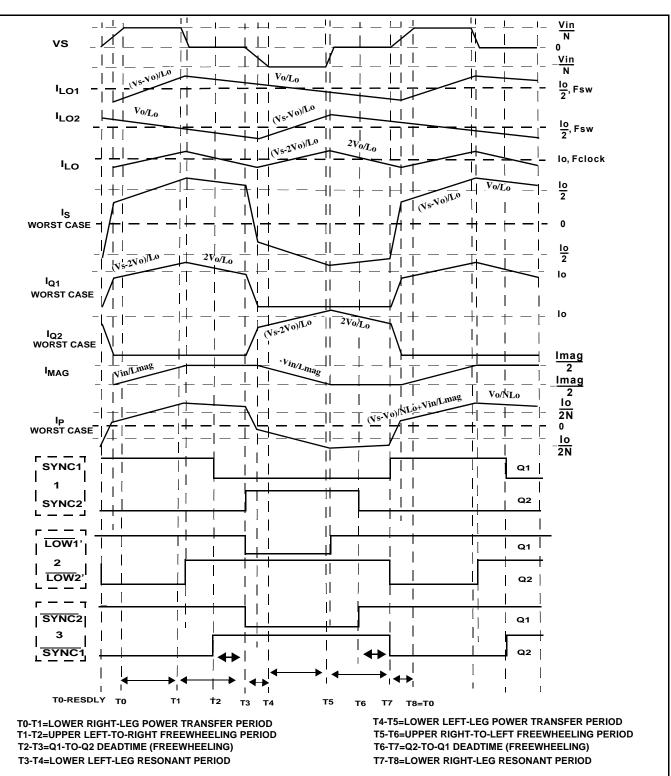

In the above Figure, 10 through 18 are exaggerated only for demonstration purposes. There are three p synchronous rectification drive schemes:

- 1. Existing Synchronous Drive Signals (Sync1 & Sync2) + Non-inverting High Current Drivers (such as MIC4422)- The Synchronous Fets (Q1 & Q2) are turned off together at the dead time and turned on alternatively every clock period;

- 2. Lower Drive Signals + Proper Delay + Inverting High Current Drivers (such as MIC4421)- The corresponding synchronous FET is turned off whenever a voltage is across the secondary winding;

- 3. Existing Synchronous Drive Signals + Inverting High Current Drivers- The synchronous FETs are turned on together at the dead time and turned on alternately every clock period.

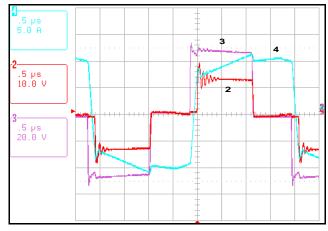

#### FIGURE 4. DRIVE SIGNALS TIMING DIAGRAM

In the above figure, T0 through T8 are exaggerated only for demonstration purposes. The slope of each waveform is in an approximation. For a more accurate representation, losses should be included. The worst case happens at only Q1 or Q2 carrying the load current during the freewheeling period. The current distribution through Q1 and Q2 is different in these three drive schemes. Case 2 is the best option since both of its synchronous FETs are turned on during the freewheeling period. Note that VS is in the case of no primary leakage inductance, otherwise, delay would be induced, as illustrated in the experimental results.

#### FIGURE 5. CURRENT WAVEFORMS

4

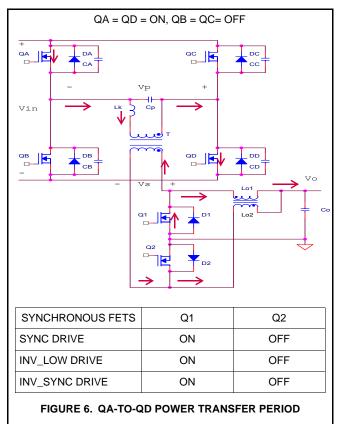

## T0 -->T1, QA-to-QD Power Transfer (Active) Period [Figure 6]

When QD is turned on, QA has been already turned on in the previous period, the resonant delay. In this transfer (active) period, the full input voltage (V\_{IN}) is across the primary of the transformer, and VIN/N is across the secondary of the transformer once the primary current catches the reflected output current. The primary current first flows from QD to QA due to the prior resonant current and then reverses in direction until the current reaches zero and starts ramping up at a rate determined by VIN, the magnetizing inductance, and the output inductance. Simultaneously, Q2 should stay off for eliminating shootthrough currents, and Q1 is turned on to reduce conduction losses; the current through the Lo2 is positive ramp, and the current through the Lo1 is negative ramp. The ON-time of QD is a function of  $V_{IN}$ , Vo, the transformer turns ratio N, and the output load lo. QD is turned off when the peak of the modified current ramp signal hits the error voltage, and the freewheeling period then begins.

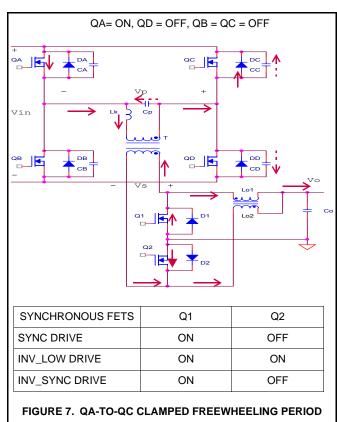

# T1 --> T2, QA-to-QC Clamped Freewheeling (Passive) Period [Figure 7]

Once QD is turned off by trailing edge pulse width modulation, the primary current continues flowing into the output capacitance (Coss) CD of QD, which will be charged up from the switch Rds(on) Drop to  $V_{\text{IN}}$  - Diode Drop. Simultaneously, the primary capacitance (Cp) of the

5

transformer and the output capacitance CC of QC are discharged to from  $V_{\mbox{\rm IN}}$  to zero voltage (~diode drop).

This transition is accomplished using the energy stored in the leakage inductance of the transformer, the magnetizing inductance, the reflected output inductance, and any external commutating inductance. After the transition, the primary current flows in the same direction and the real freewheeling period begins. One end of the transformer is shorted to VIN by the channel of QA, and the other end is clamped to  $V_{IN}$  by the body diode of QC, which is the only path that the primary current can go through. The losses due to the body diode conduction at the freewheeling period could be significant if the primary current (the lumped sum of the magnetizing current and the reflected secondary winding freewheeling current), is relatively high. These conduction losses can be minimized by employing the maximum allowable turns ratio of the main transformer, i.e, the maximum allowable duty cycle in the design. In some applications, shunting upper switches with Schottky diodes might be another possible way to reduce the conduction losses. For a wide range input application, if a pre-regulator is implemented, then a fixed, high duty cycle (~100%) post full-bridge regulator can be achieved and the freewheeling time is minimized. The power dissipation of the upper FETs can be therefore reduced significantly.

Three different synchronous rectification drive schemes can be implemented with the ISL6551 as shown in Figures 4 and 5. The INV\_LOW DRIVE scheme is the one that would provide an additional path for the secondary freewheeling current since both Q1 and Q2 are turned on during the freewheeling time, which could reduce the conduction losses and the reflected output current in the primary. The amount of the load current split into Q1 and Q2 depends on the voltage drop across the secondary winding, the Rds(on) of Q1 & Q2, and/or the body diode drop of Q1 & Q2. The optimum performance of the converter happens when the load current is split into both turned-on Q1 and Q2 evenly. In reality, the body diode drop at one of upper FETs, the leakage inductance, and the shorted primary winding force one of the synchronous FETs to carry the majority of the output current while the other conducts a minority of the load.

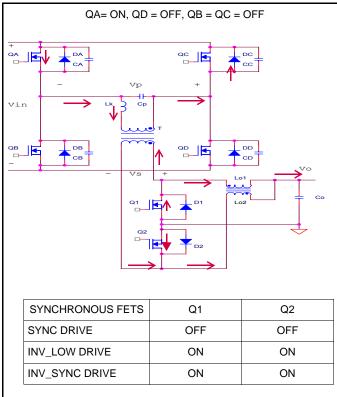

# T2 --> T3, Q1-to-Q2 Dead Time Period [Figure 8]

#### FIGURE 8. Q1-TO-Q2 DEAD TIME PERIOD

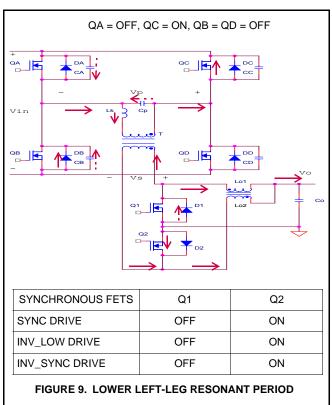

The dead time is used to prevent simultaneous conduction of QC and QD, which would cause shoot-through currents. The dead time is still part of the freewheeling period. The drive control signals for the power switches therefore do not change states while the drive signals of the synchronous FETs change levels. In the SYNC DRIVE scheme, both Q1 and Q2 now are turned off and the load current freewheels through the body diodes of both FETs. This introduces high conduction losses in high output current applications. Shunting both synchronous FETs with schottky diodes can reduce the losses. In the INV\_SYNC DRIVE scheme, both Q1 and Q2 are turned on, therefore, schottky diodes are not required, so are not in the INV\_LOW DRIVE scheme. T3 --> T4, Lower Left-Leg (QB) Resonant Period [Figure 9]

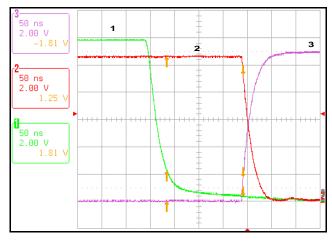

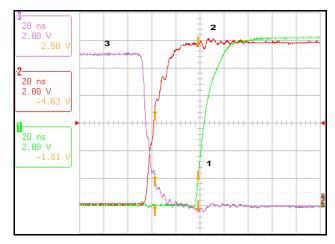

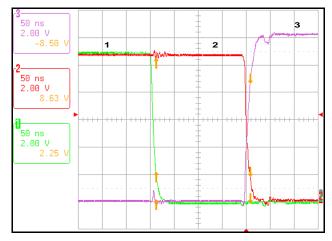

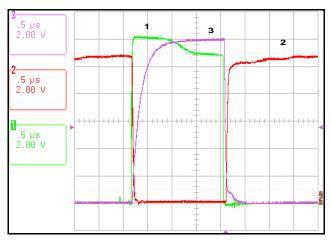

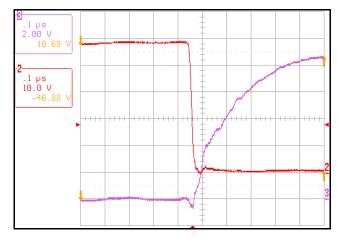

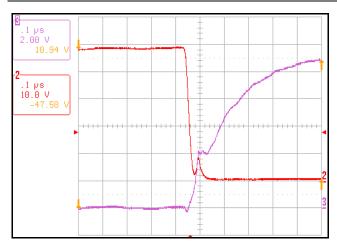

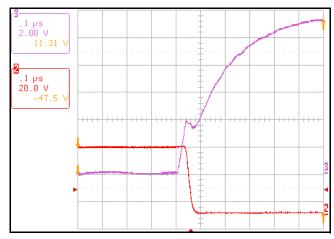

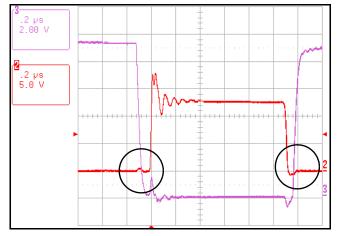

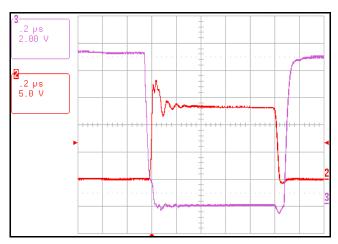

The dead time period is followed by the lower left-leg resonant period. It begins with QA turned off and QC turned on. At the beginning of this transition, the input voltage is applied first across the commutating inductance (leakage and any external inductances), i.e, the real primary stays zero until the current through these inductors changes in direction in the next time interval. This can be seen in the voltage waveforms across the primary winding and the secondary winding, discussed in the EXPERIMENTAL RESULTS section on pages 24-25. The direction of the current through the primary winding remains the same as that in the previous time interval. The current flows into the transformer primary capacitance (Cp) and the output capacitance (Coss) CA of QA, which will be charged up from zero voltage (~Rds(on) Drop) to VIN. Simultaneously, the output capacitance CB of QB is discharged to from VIN-Rds(on) Drop to zero voltage (~diode drop). This transition is accomplished with the energy stored in the primary inductance (including leakage inductance, magnetizing inductance, and any external inductance). It takes a longer time to complete this transition than the one reaching the freewheeling period since the energy stored in the resonant inductances decreases due to the conduction losses of the power switches and the primary current is decaying in the freewheeling period. Once QB is clamped to zero voltage by its own body diode, QB is turned on at zero voltage (ZVS transition). Another power transfer period is followed by the other diagonal power switches (QC-to-QB). The rest of the

discussion (Figures 10 to 13) is just the repetition of another half cycle.

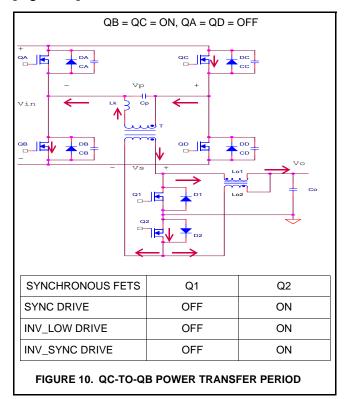

# T4 --> T5, QC-to-QB Power Transfer Period [Figure 10]

When QB is turned on, QC has been already turned on in the previous period, the resonant delay. In this transfer (active) period, the full input voltage ( $V_{IN}$ ) is across the primary of the transformer, and VIN/N is across the secondary of the transformer once the primary current catches the reflected output active current. The primary current first flows from QB to QC due to the prior resonant current and then reverses in direction until the current reaches zero and starts ramping up at a rate determined by VIN, the magnetizing inductance, and the output inductance. Simultaneously, Q1 should stay off for eliminating shootthrough currents, and Q2 is turned on to reduce conduction losses; the current through the Lo1 is a positive ramp, and the current through Lo2 is a negative ramp. The ON-time of QB is a function of  $V_{IN}$ , Vo, the transformer turns ratio N, and the output load lo. QB is turned off when the peak of the modified current ramp signal hits the error voltage, and another freewheeling period then begins.

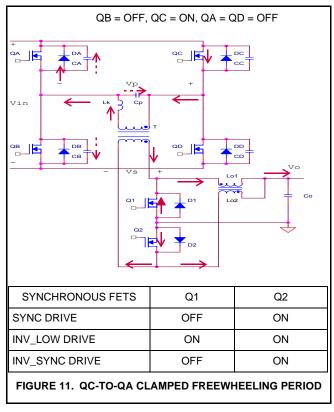

# T5 -->T6, QC-to-QA Clamped Freewheeling Period (Passive) [Figure 11]

Once QB is turned off, the primary current continues flowing into the output capacitance (Coss) CB of QB, which will be charged up from the switch Rds(on) Drop to  $V_{IN}$  + Diode Drop. Simultaneously, the primary capacitance (Cp) of the transformer and the output capacitance CA of QA are

7

discharged from V<sub>IN</sub> to zero voltage (~diode drop). This transition is accomplished using the energy stored in the leakage inductance of the transformer, the magnetizing inductance, the reflected output inductance, and any external commutating inductance. After the transition, the primary current flows in the same direction and the real freewheeling period begins. One end of the transformer is shorted to V<sub>IN</sub> by the channel of QC, and the other end is clamped to V<sub>IN</sub> by the body diode of QA, which is the only path that the primary current can go through. Refer to the T1-->T2 period for more detailed discussion.

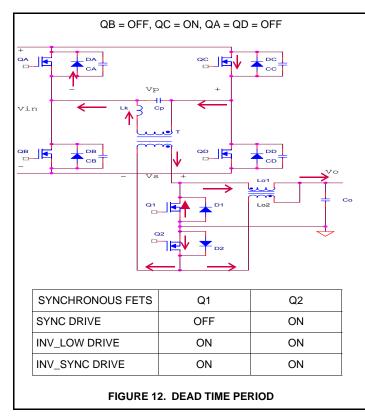

# T6 --> T7, Q2-to-Q1 Dead Time Period [Figure 12]

The dead time is used to prevent simultaneous conduction of QA and QB, which would cause shoot-through currents. The dead time period is still part of the freewheeling period, the drive control signals for the power switches therefore do not change states while the drive signals of the synchronous FETs change levels. In the SYNC DRIVE scheme, both Q1 and Q2 now are turned off, the load current free wheels through the body diodes of both FETs, which introduces high conduction losses in high output current applications. Shunting both synchronous FETs with schottky diodes can reduce the losses. In the INV\_SYNC DRIVE scheme, both Q1 and Q2 are turned on, therefore, schottky diodes are not required, so are not in the INV\_LOW DRIVE scheme.

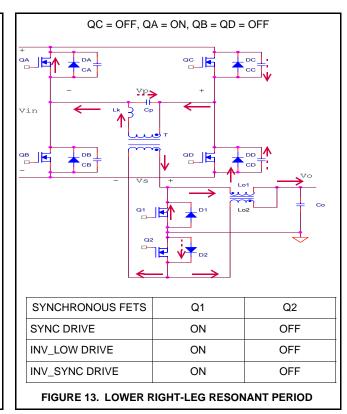

# T7 --> T8=To, Lower Right-Leg (QD) Resonant Period [Figure 13]

The previous dead time period is followed by the lower rightleg resonant period. It begins with QC turned off and QA turned on. At the beginning of this transition, the input voltage is applied first across the commutating inductance (leakage and any external inductances), i.e., the real primary stays zero until the current through these inductors changes in direction in the next time interval. This can be seen in the voltage waveforms across the primary winding and the secondary winding, discussed in the EXPERIMENTAL *RESULTS* section on page 24-25. The direction of the current through the primary winding remains the same as that in the previous time interval. The current flows into the transformer primary capacitance (Cp) and the output capacitance (Coss) CC of QC, which will be charged up from zero voltage (~Rds(on) Drop) to VIN. Simultaneously, the output capacitance CD of QD is discharged to from VIN-Rds(on) Drop to zero voltage (~diode drop). This transition is accomplished with the energy stored in the primary inductance (including leakage inductance, magnetizing inductance, and any external inductance). It takes a longer time to complete this transition than the one reaching the freewheeling period since the energy stored in the resonant inductance decreases due to the conduction losses of the power switches and the primary current is decaying in the freewheeling period. Once QD is clamped to zero voltage by its own body diode, QD is turned on at zero voltage (ZVS transition). At this point a full operating cycle is completed.

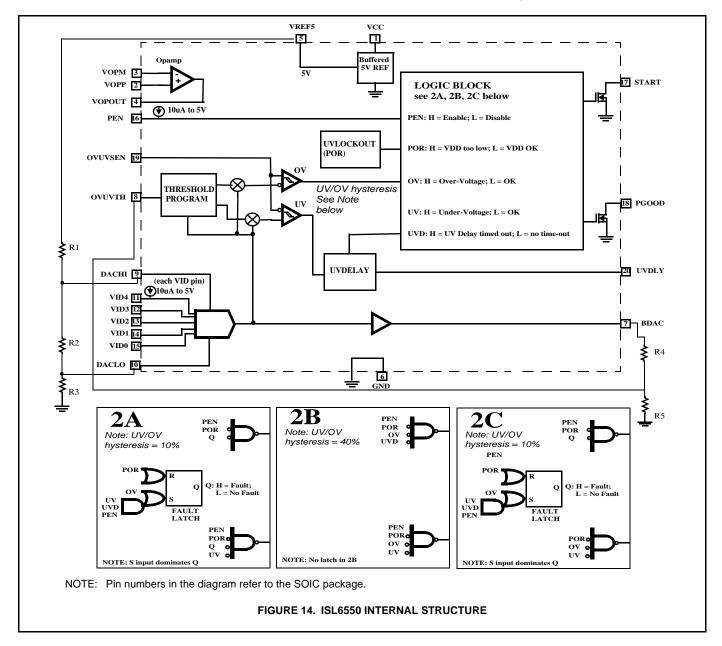

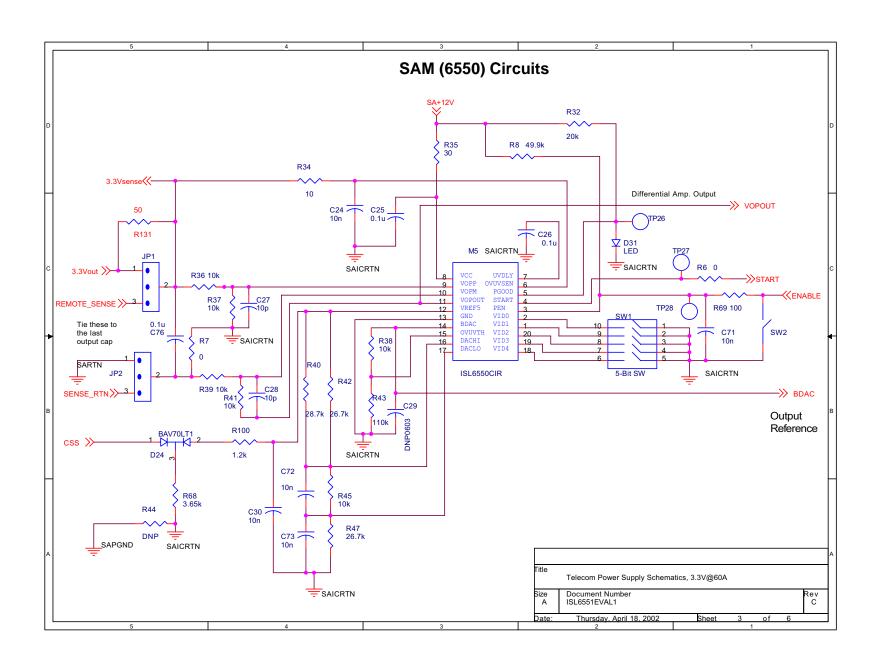

# Intersil Supervisor and Monitor: ISL6550

The ISL6550 is a precision flexible, VID-code-controlled reference and voltage monitor for high-end microprocessor and memory power supplies. It monitors various input signals, and supervises the systems with its outputs. The ISL6550 saves board space, design time, and system cost. The internal structure of the ISL550 is shown in Figure 14. The reference design is implemented with the MLFP-packaged ISL6550, **C** version. Refer to the device datasheet for operating details.

In the reference design, the ISL6550 monitors the output voltage and supervises the ISL6551 full bridge controller.

- The spare operational amplifier of the ISL6550 is used as a differential amplifier and its output (VOPOUT) is sent to the inverting input (EAI) of the error amplifier of the ISL6551. Note that the VOPOUT is limited to 5V.

- The under-voltage delay (UVDLY) prevents false triggering of the START output during startup, and the ISL6550 START output is fed to the ON/OFF input of the ISL6551. In output over-voltage (+8.33%) and undervoltage (-8.33%) conditions, the START is triggered and latches shutdown the ISL6551 controller. When the VCC of ISL6550 is below the turn-on/off threshold, the START is held low and disables the ISL6651 controller.

- The output reference BDAC, which is fed to the noninverting input (EANI) of the error amplifier of the ISL6551, is programmed by the 5-bit VIDs and the resistor network that connects to DACHI and DACLO. Note that a 50k total resistance of the network is recommended and the overall

8

output error should include VREF5 error and external resistor divider error as well as the internal buffer offset. In the reference design, the output voltage can be programmed from 2.64V to 3.63V with 31.918mV step and +/-3% statics error over full operating conditions.

The output voltage is sensed by the OVUVSEN, and the OV-UV windows is centered around the BDAC voltage and can be programmed with the OVUVTH pin from +/-5% to +/-40% about the BDAC voltage. In the reference design, the over/under voltage window is set at +/-8.33%.

- PEN is connected to a mechanical switch to turn on/off the converter manually. It is also controlled by the circuitries that monitor the input voltage level and the thermal condition of the converter.

- PGOOD provides an indication if the output voltage is within over/under voltage limits (+/-8.33%).

# **Converter Design**

This section presents a step-by-step design procedure for a 48V-to-3.3V, 200W, 470kHz with 88% efficiency converter using both ISL6551 and ISL6550 for telecom applications (i.e  $V_{IN}$ =36V-to-75V). The converter is designed with secondary-referenced, peak current-mode control, and both ZVS full bridge and current doubler topologies.

For simplicity, all calculations in this section neglect the transitions shown in Figure 5. The worst case current waveforms are used even in the INV\_LOW DRIVE scheme, unless otherwise stated.

# Select Synchronous DRIVE Scheme

The INV\_LOW DRIVE scheme for synchronous rectification is employed in the reference design. This scheme induces less conduction losses in the synchronous FETs than both INV\_SYNC and SYNC DRIVE schemes, which can be explained with a few equations (EQ. 1- 6). The terms used in all equations are defined later in the paper, unless otherwise stated in the text.

$$lo^{2} = (lQ1 + lQ2)^{2} = lQ1^{2} + lQ2^{2} + 2 \cdot lQ1 \cdot lQ2$$

(EQ. 1)

$$IQ1^{2} + IQ2^{2} \le IQ1^{2} + IQ2^{2} + 2 \bullet IQ1 \bullet IQ2$$

(EQ. 2)

The power dissipation is the same in the active (transfer) period but different in the freewheeling period for the three drive schemes. In both INV\_SYNC and SYNC DRIVE schemes, only one synchronous FET is turned on carrying all the load current during the freewheeling period. The conduction losses of each leg in the freewheeling period can be approximated with EQ. 3:

$$Psynfetfr = Io^{2} \bullet \left(\frac{1-D}{2}\right) \bullet Rdsonsyn$$

(EQ. 3)

In the INV\_LOW DRIVE scheme, both synchronous FETs are turned on and each one carries a portion of the load current during the freewheeling period. The power dissipation of each leg in this period is reduced to EQ. 4:

$$Psynfetfr = (IQ1^2 + IQ2^2) \bullet \left(\frac{1-D}{2}\right) \bullet Rdsonsyn$$

(EQ. 4)

Comparing EQ. 3 to EQ. 4, we note that the INV\_LOW scheme induces less power dissipation in the synchronous FETs by an amount of EQ. 5:

$$\Delta P synfet fr = 2 \bullet IQ1 \bullet IQ2 \bullet (1 - D) \bullet R dsonsyn$$

(EQ. 5)

In addition, the INV\_LOW scheme also helps cut down the conduction losses in the primary FETs since the primary has less reflected secondary current, which decreases with the difference between IQ1 and IQ2, as shown in EQ. 6:

$$Ip \approx \frac{Is}{N} = \frac{IQ1 - IQ2}{2N}$$

(EQ. 6)

Although the INV\_LOW scheme is a better choice from the power dissipation standpoint, the user should pay special attention to the impact of having on overlap between both synchronous FETs during the freewheeling period in current share, light load, start up, and turn-off operations. Some discussions are presented in the *EXPERIMENTAL RESULTS* section.

### Select Switching Frequency and Define Maximum Available Duty Cycle

Several things are considered when selecting an appropriate switching frequency for a particular application. The size of the converter (limited by sizes of magnetics components), the overall losses of magnetics components, the switching losses of power MOSFETs, the desired efficiency, the transient response, and the maximum achievable duty cycle are all considerations. An iterative process is required, monitoring changes of the above parameters, to obtain an optimum switching frequency for a particular application. Users can use equations presented in this paper to design a MathCAD worksheet, which will help obtain a rough idea of the range of optimum frequencies for their applications. Note that the higher the switching frequency is, the higher the loop bandwidth (typical 1/10 or higher of the switching frequency) can be realized, but the lower the maximum duty cycle is available.

In the initial design of the evaluation board, these parameters are pre-selected: Fsw=250kHz=Fclock/2, t<sub>DEAD</sub>=200ns, and t<sub>RESDLY</sub>=100ns. The maximum available duty cycle then can be calculated using EQ. 7 (Dmaxav=85%). The duty cycle defined in this application note is the ratio of the ON-time interval of a lower FET to one clock period.

$$Dmaxav = \left(1 - \frac{t_{DEAD} - t_{RESDLY}}{Fclock}\right)$$

(EQ. 7)

# Define Turns Ratio

The primary-to-secondary turns ratio of the main transformer should be chosen as high as possible without exceeding the maximum available duty cycle (Dmaxav=0.85) at the minimum line (Vinmin=36V, or the input UV setpoint) and the rated load (Io=60A) situation. The higher the turns ratio is, the less the load current is reflected to the primary side, and the less the power losses are induced by the primary MOSFETs. The maximum allowable turns ratio can be calculated with EQ. 8 (Nmax=3.79).

$$Dmaxav = \frac{2 \cdot (Vomax + Vmisc + Vsynfet) \cdot N}{\left(Vinmin - Rdsonpri \cdot \frac{lo}{N}\right) - Vsynfet \cdot N}$$

(EQ. 8)

where Vsynfet = Io x Rdsonsyn/2 is the channel drop of the synchronous FETs at half of the load (assuming that the output load is split evenly into both synchronous FETs during the freewheeling period), Vomax is the maximum output voltage (3.63V), and Vmisc is the sum of the miscellaneous voltage drops including contact resistance, winding resistance, PCB copper resistance. The initial guess of Vmisc is 0.3V for having a safe margin. If the load (lo) conducts through only one synchronous FET during the freewheeling period, then EQ. 8 can be simplified to EQ. 9 (Nmax=3.77):

$$Dmaxav = \frac{2 \cdot (Vomax + Vmisc + 2 \cdot Vsynfet) \cdot N}{Vinmin - Rdsonpri \cdot \frac{lo}{N}}$$

(EQ. 9)

With the assumptions of Rdsonpri= $25 \times 1.2 m\Omega$  (Tj= $50^{0}$ C) and Rdsonsyn= $1.125 \times 1.13 m\Omega$  (Tj= $50^{0}$ C), EQ. 9 produces Nmax=3.77. Since the size and height of the converter are limited to that of a telecom half brick, a planar transformer with a low number of turns on both the primary and secondary sides is required. Therefore, 7/2 and 11/3 turns ratio are preferred choices. A transformer with 7 primary turns and 2 secondary turns has been used in the reference design due to the availability of magnetic cores in stock. In fact, a transformer with 11/3 turns ratio is generally recommended.

#### **Output Filter Design (Current Doubler)**

The output L-C filter is normally defined based on requirements of the output ripple voltage (70mV) and the transient response (dVtr=150mV). In general, if the requirement of the transient response is met, then the output ripple voltage will be within the limit.

As a rule of thumb, the overall ripple current (dlo) should be no more than 20% of the rated load, and the output inductor value (for each one) can be defined by EQ. 10:

$$Lo = \frac{2 \bullet (Vo + 2 \bullet Vsynfet) \bullet (1 - D)}{dIo \bullet Fclock}$$

(EQ. 10)

The ripple current (dl) through each inductor can be calculated with EQ. 11:

$$dI = \frac{(Vo + 2 \bullet Vsynfet) \bullet (2 - D)}{Lo \bullet Fclock}$$

(EQ. 11)

The requirement of the transient response is the major factor of defining the maximum overall ESR of the output capacitors in EQ. 12. Note that this converter is designed to meet 150mV transients (dip/overshoot) for a 25% rated load step (ESR <  $10m\Omega$ ).

$$ESR < \frac{dVtr}{lstep}$$

(EQ. 12)

The minimum required output capacitance (Co) can be estimated by EQ. 13 when limiting the output ripple voltage contributed by output capacitance to be no more than  $dV_{Co}$ .

$$Co = \frac{1}{dV_{Co}} \bullet \frac{dIo}{8 \bullet Fclock}$$

(EQ. 13)

In addition to meeting the requirements of ESR and Co, the output capacitors should be able to absorb the output RMS current, as defined in EQ. 14.

lorms =

$$\frac{dIo}{\sqrt{12}}$$

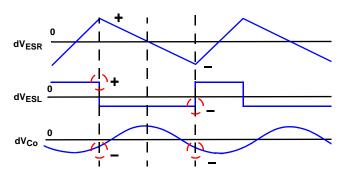

(EQ. 14)

The output voltage ripple can be conservatively approximated by EQ. 15. The first two terms (dV<sub>ESR</sub> and dVESL) contributed by the equivalent series resistance (ESR) and the equivalent series inductance (ESL) of the output capacitors are the dominant ones and are normally accurate enough to estimate the ripple voltage. The last term (dV<sub>Co</sub>) contributed by the output capacitance (Co) is normally much smaller and can be neglected since the peak of the dV<sub>Co</sub> happens at the ripple current across zero and does not align with the peak of dV<sub>ESR</sub>, as shown in Figure 15. The positive and negative peaks of the overall ripple voltage (sum of all three components) relative to the DC level is not symmetric (caused by  $dV_{Co}$  and  $dV_{ESL}$ ) unless the converter operates at 50% duty cycle. This asymmetry between positive and negative peaks is not a big concern in most applications since both dV<sub>Co</sub> and dV<sub>FSI</sub> are generally very small compared to the ESR portion. Note that the DC level remains constant. Refer to [6] for more details.

$$Voripple \approx dlo \bullet ESR + \frac{ESL}{Lo}Vs + \frac{1}{Co} \bullet \frac{dlo}{8 \bullet Fclock}$$

(EQ. 15)

FIGURE 15. OUTPUT RIPPLE VOLTAGE COMPONENTS

The ESL of a capacitor is not usually listed in databooks. It can be practically approximated with EQ. 16:

$$\mathsf{ESL} = \frac{1}{\mathsf{Co}} \bullet \frac{1}{(2\pi \bullet \mathsf{Fres})^2} \tag{EQ. 16}$$

where Fres is the resonant frequency that produces the lowest impedance of the capacitor.

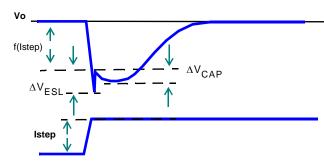

At the very edge of the transient, the equivalent ESL of all output capacitors induces a spike, as defined in EQ. 17 for a

given dl/dt, that adds on the top of the existing voltage undershoot/overshoot due to the ESR and capacitance.

$$\Delta V_{ESL} = ESL \bullet \frac{dI}{dt}$$

(EQ. 17)

FIGURE 16. TYPICAL TRANSIENT RESPONSE WAVEFORM

Thus, the overall output voltage undershoot/overshoot due to load transients can be summarized in EQ. 18, in which the last term can be normally dropped out if the very edge of the transient is the dominant peak, as shown in Figure 16.

$$dVtr \approx f(Istep) + \Delta V_{ESL} + \Delta V_{CAP}$$

(EQ. 18)

where

$$\begin{split} f(\text{Istep}) &= \text{Istep} \frac{\sqrt{1 + (2\pi \bullet f_c \bullet \text{Co} \bullet \text{ESR})^2}}{2\pi \bullet f_c \bullet \text{Co}} \\ f(\text{Istep}) &\approx \text{Istep} \bullet \text{ESR} \quad \text{for} \quad fc \geq \frac{1}{2\pi \bullet \text{ESR} \bullet \text{Co}} \\ f(\text{Istep}) &\approx \frac{\text{Istep}}{2\pi \bullet f_c \bullet \text{Co}} \quad \text{for} \quad fc \leq \frac{1}{2\pi \bullet \text{ESR} \bullet \text{Co}} \\ \Delta V_{\text{CAP}} &= \Delta V_{\text{HUMP}} \quad \text{for} \quad \text{step-up transients} \\ \Delta V_{\text{CAP}} &= \Delta V_{\text{SAG}} \quad \text{for} \quad \text{step-down transients} \end{split}$$

The last term in EQ. 18 is a direct consequence of the amount of output capacitance. After the initial spike, all the excessive charge is dumped into the output capacitors on step-down transients causing a temporary hump at the output, and the output capacitors deliver extra charge to meet the load demand on step-up transients causing a temporary sag before the output inductors catch the load. The approximate response time intervals for removal and application of a transient load are defined by dTn and dTp, respectively.

$$\Delta V_{\text{HUMP}} = \frac{\text{Istep} \cdot \text{dTn}}{2 \cdot \text{Co}}$$

(EQ. 19)

where

$$dTn = Lo \frac{Istep}{2Vo}$$

$$\Delta V_{\mathsf{SAG}} = \frac{\mathsf{lstep} \cdot \mathsf{dTp}}{2 \cdot \mathsf{Co}}$$

(EQ. 20)

where

$$dTp = Lo \frac{Istep}{Vs - 2Vo}$$

In low-profile, high current density, and high frequency applications, the required output capacitance defined in EQ. 13 might not be enough to deliver or absorb energy due to load transients. This could cause a significantly large undershoot/overshoot at the output. In the reference design, the loop bandwidth ( $f_c$ ) is lower than the zero [1/( $2\pi$ \*ESR\*Co)] of the output capacitors, which have low ESL transient component due to low dl/dt(1A/us), therefore, the required output capacitance can be roughly approximated with EQ. 21 [7].

$$Co \approx \frac{Istep}{2\pi \bullet f_c \bullet dVtr}$$

$fc \leq \frac{1}{2\pi \bullet ESR \bullet Co}$  (EQ. 21)

Several lower-profile TAIYO YUDEN 100u, 6.3V capacitors (JMK212F107MM) have been used in the evaluation board to meet the electrical requirements of the above discussion and the height constraint of the converter.

Besides ESL, ESR, and capacitance of the output capacitors, other system parasitics such as board resistance and inductance should be included in the load transient analysis [6], which will not be discussed in this paper.

Electrical design parameters of the output inductors are summarized in EQs. 11, 22, & 23, which specify the ripple current, the peak current, and the RMS current of each inductor.

$$\mathsf{lindpeak} = \frac{\mathsf{lo} + \mathsf{dI}}{2} \tag{EQ. 22}$$

lindrms =

$$\frac{lo}{2} + \frac{dl}{\sqrt{12}}$$

(EQ. 23)

#### Calculations for Synchronous FETs (Q1 & Q2)

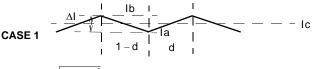

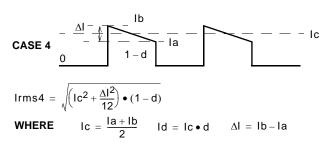

Some fundamental formulas that are used to calculate RMS values of triangular and trapezoid waveforms and to derive most equations in this paper are defined below.

$$Irms1 = \sqrt{Ic^2 + \frac{\Delta I}{12}}$$

rms2 =

$$\sqrt{\left(1c^2 + \frac{\Delta}{1}\right)}$$

In the power transfer period, one synchronous FET is turned off, and the other one is turned on conducting all the load

current. The peak current through the FET is defined by the load current plus half of the output ripple current in EQ. 24. In this period, the RMS current through each FET can be calculated with EQ. 25 using Case 2 formula. Note that the duty cycle (D) is defined as the ratio of the ON-time interval of a lower FET over one clock period (twice of the switching period), which explains the 1/2 factor in the equation.

$$lsynpeak = lo + \frac{dlo}{2}$$

(EQ. 24)

$$Isynrmstr = \sqrt{\left(Io^2 + \frac{dIo^2}{12}\right) \bullet \frac{D}{2}}$$

(EQ. 25)

In the worst case, all the load current flows through one of the synchronous FETs during the freewheeling period (including the resonant and dead periods for simplicity), the RMS current through the FET can be estimated by EQ. 26.

$$Isynrmsfr = \sqrt{\left(Io^2 + \frac{dIo^2}{12}\right) \cdot \frac{1-D}{2}}$$

(EQ. 26)

Thus, the overall RMS current through one synchronous FET can be defined in EQ. 27, while the conduction losses of each synchronous FET can be calculated with EQ. 28.

$$|synrms| = \sqrt{|sysrmstr^2 + |sysrmsfr^2|}$$

(EQ. 27)

$$Psynfet = Isynrms^2 \bullet Rdsonsyn$$

(EQ. 28)

As shown in EQs. 25 and 26, the higher the ripple current is, i.e., the lower the output inductances are, the higher the RMS currents are, and the higher the conduction losses of the synchronous FETs are.

In addition, the distribution factor ( $F_{DIST}$ ) for IQ1 and IQ2 currents during the freewheeling period for the INV\_LOW DRIVE scheme can be included in EQ. 26 for an accurate calculation:

$$F_{\text{DIST}} = \sqrt{(1-p)^2 + p^2}$$

(EQ. 29)

where p is the percentage of load current through one of the synchronous FETs. A guess of p can made by looking at the primary freewheeling current, as shown in the

EXPERIMENTAL RESULTS section. For the other two drive schemes,  $\mathsf{F}_{\text{DIST}}$  is one.

In the SYNC DRIVE scheme, both synchronous FETs are turned off during the dead time period. The freewheeling

current flows through the body diodes of the FETs, and any external schottky diodes. In the worst case, the freewheeling current flows through only one leg, and the average current for the dead time can be estimated by EQ. 30, where  $t_{DEAD}$  is the dead time and  $t_{RESDLY}$  is the resonant time.

Isyndeadavg =

$$\frac{t_{DEAD}}{4 \bullet T} \left( Io + \frac{dIo(t_{DEAD} + t_{RESDLY} - 0.5T(1 - D))}{(1 - D) \bullet T} \right)$$

(EQ. 30)

An additional term "*Isyndeadavg x Vdsyn*" should be added to EQ. 28 if the SYNC DRIVE scheme is implemented. *Isynrmsfr* however would be slightly smaller.

The maximum voltage across the synchronous FET can be approximated with EQ. 31, adding 30% margin for the ringing on the rising edge.

$$Vsynmax = \frac{Vinmax}{N}(1+0.3)$$

(EQ. 31)

The synchronous FETs should be selected such that the  $V_{DS}$  rating and power rating of the MOSFETs are greater than *Vsynmax* and *Psynfet*, respectively. Four 30V Siliconix Si4842DY MOSFETs are used for each leg. Note that any switching losses, which will be discussed later, should be included in the calculation to define the maximum power dissipation.

# Calculations for Primary Switches (QA, QB, QC, & QD)

The peak current through the primary winding happens at the end of the active period, as defined in EQ. 32

$$lpripeak = \frac{lo+dl}{2N} + \frac{lmag}{2}$$

(EQ. 32)

$$Imag = \frac{(Vin - 2 \bullet Ip \bullet Rdsonpri) \bullet D}{Lmag \bullet Fclock}$$

(EQ. 33)

EQ. 33 defines the peak-to-peak magnetizing current. The RMS current through the power switches in the active period can be estimated by EQ. 34, which also defines the overall RMS current through a lower FET.

$$Iprirmstr = \sqrt{\left(\left(\frac{Io}{2N}\right)^2 + \frac{dIp^2}{12}\right) \bullet \frac{D}{2}}$$

(EQ. 34)

where  $dIp = \frac{dI}{N} + Imag$

If there is a time delay Td to turn on the lower FET after its output capacitance is completely discharged, i.e, the resonant delay is set longer than is necessary, then the current will flow through the body diode of the lower FET, which has an average value defined in EQ. 35.

$$lpriavgres = \left(\frac{lo}{2N} + \frac{lmag}{2} + \frac{dl(D + Td/T)}{2N(2-D)}\right) \bullet \frac{Td}{2T}$$

(EQ. 35)

The freewheeling current flows through the channel and the body diode of upper FETs in alternate freewheeling periods and at alternate directions. The RMS current through the channel can be calculated with EQ. 36. The average current through the body diode of the upper FET can be estimated with EQ. 37.

$$Iprirmsfr = \sqrt{\left(\left(\frac{Io}{2N} + \frac{dI}{2N(2-D)} + \frac{Imag}{2}\right)^2 + \frac{dI^2(1-D)^2}{12N^2(2-D)^2}\right) \bullet \frac{1-D}{2}}$$

(EQ. 36)

$$Ipriavgfr = \left(\frac{Io}{2N} + \frac{Imag}{2} - \frac{dI}{2N(2-D)}\right) \bullet \frac{1-D}{2}$$

(EQ. 37)

Thus, the overall RMS current through the channel of each upper FET is defined in EQ. 38:

$$lprirms = \sqrt{lprirmstr^2 + lprirmsfr^2}$$

(EQ. 38)

With all the above RMS and average current information, the conduction losses of each power switch can be roughly estimated with EQs. 39 and 40. As shown in EQs. 34 and 36, the higher the inductor ripple current and the magnetizing current are, i.e., the lower the output inductance and the magnetizing inductance are, the larger the RMS currents are, the higher the power losses would be induced by the primary switches.

$$Pupfet = Iprirms^{2} \bullet Rdsonpri + Ipriavgfr \bullet Vd$$

(EQ. 39)

$$Plowfet = Iprirmstr^2 \bullet Rdsonpri + Ipriavgres \bullet Vd$$

(EQ. 40)

Four 100V Siliconix SUD40N10 MOSFETs are selected for the bridge switches such that the ratings of the device are greater than *Pupfet, Plowfet,* and the *maximum input voltage.* Note that any switching losses, which will be discussed later, should be included in EQs. 39 and 40 to define the maximum power dissipation of the primary switches, which limits the MOSFET selection.

## Input Filter Design

The input pulsating current filtered by the input capacitors has an RMS value in EQ. 41, while the minimum required input capacitance is defined in EQ. 42.

linrms =

$$\sqrt{\left(\frac{lo}{2N}\right)^2 \cdot (D - D^2) + \frac{(dlp)^2}{12} \cdot D}$$

(EQ. 41)

$$Cin = \frac{lo}{2N} \bullet (D - D^2) \bullet \frac{T}{dVincap}$$

(EQ. 42)

The dV<sub>IN</sub>cap is the acceptable input ripple voltage contributed by the amount of input capacitance, of which is the input capacitors (ITW Patron capacitors in the reference design) that filter most of pulsating currents. The maximum value of EQ. 41 happens at D~0.5, while the maximum value

of EQ. 42 happens at D=0.5. Several lower-profile ITW Paktron capacitors (105K100ST2814) and an external capacitor have been used in the evaluation board. If a hold up time ( $t_{HOLDUP}$ ) is required when the input line is momentarily disconnected, then EQ. 43 helps define the required hold up capacitance:

$$\begin{split} \text{Cin} &= \frac{2\text{Po} \bullet t_{\text{HOLDUP}}}{\eta \bullet (\text{Vin}^2 - \text{V}^2_{\text{HOLDUP}})} \end{split} \tag{EQ. 43} \\ \text{or} \qquad & \text{Cin} \approx \frac{\text{Po} \bullet t_{\text{HOLDUP}}}{\eta \bullet \text{Vin} \bullet \Delta \text{Vin}} \\ \text{where} \qquad & \eta = \text{Efficiency} \\ & \Delta \text{Vin} = \text{Vin} - \text{V}_{\text{HOLDUP}} \end{split}$$

The overall input voltage ripple induced by the ESR and capacitance of the input capacitors can be estimated with EQ. 44. In addition, the spikes caused by the ESL of the input capacitors should be decoupled with lower ESL ceramic capacitor.

Vinripple =

$$\frac{Io}{2N} \bullet (D - D^2) \bullet \frac{T}{Cin} + ESRin \bullet Ipripeak$$

(EQ. 44)

Furthermore, for a low EMI level performance, an additional L-C filter might be required in the front end. However, the combination of both ZVS full bridge and current doubler topologies helps reduce the size of this input EMI filter.

#### Switches Losses and Driver Losses

In general, switching losses are an insignificant portion compared to conduction losses of the power switches if ZVS transitions are achieved. Since the commutating inductances store the peak energy to swing the output capacitance of the upper FET from  $V_{IN}$  to zero volt at the beginning of the freewheeling period before the upper FET is turned on, therefore, the upper FETs are lossless at turn on transitions. At the end of freewheeling period, the commutating inductances store the least energy, which might not be enough (especially in high line and/or low load conditions) to swing the output capacitance of the lower FET to zero volt before they are turned on. The turn-on losses of the lower FETs can be approximated with EQ. 45. The turn-off losses of primary switches can be minimized with a high speed driver such as Intersil HIP2100.

$$Ppriswon = \frac{1}{2}V_{on} \bullet I_{on} \bullet Fsw \qquad (EQ. 45)$$

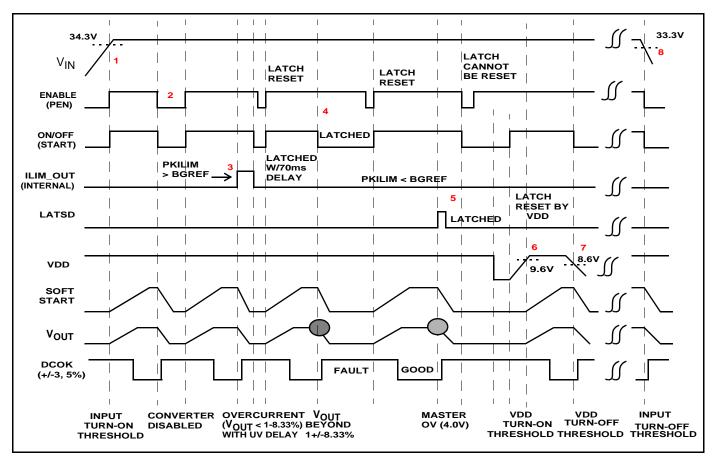

When the lower FET is turned off, its corresponding upper FET is clamped to  $V_{IN}$  in a very short time. The corresponding synchronous FET is turned on when the voltage across the secondary winding vanishes, therefore, there are no turn-on switching losses for the synchronous FETs. The resonant delay and the delay caused by the leakage inductance to have any voltage across the secondary winding, as illustrated in EXPERIMENTAL RESULTS, prior to turn off the synchronous FET, help to achieve ZVT for the synchronous FETs at turn off. To achieve ZVT as discussed in previous lines, the synchronous FET drivers however should have high current capability with little propagation delays such as MICREL 9A MIC4421 inverting drivers or better. The conduction losses and reverse recovery losses of body diodes of the synchronous FETs at turn on or off are not discussed here, but they do show up in Figure 35.

Note that the drivers with high current capability can shorten the transition time and reduce the switching losses.

The driver losses due to the gate charge of the MOSFETs should be investigated thoroughly to prevent over stressing. The switching losses of both primary and secondary drivers and its corresponding average driver current due to the gate charge can be estimated with EQs. 46 and 47, respectively,

$$Pdr = \frac{Qg}{V_{GS}} \bullet Vcc^2 \bullet Fsw$$

(EQ. 46)

$$Idr = \frac{Qg}{V_{GS}} \bullet Vcc \bullet Fsw$$

(EQ. 47)

where Qg and  $V_{GS}$  are defined in the MOSFET datasheet.

#### Define Requirements of Main Transformer

This section summarizes major design requirements of the main transformer at the switching frequency.

The turns ratio of the transformer is derived from EQ. 9 while EQ. 32 defines the peak current through the primary winding. The RMS current through the primary winding is defined in EQ. 48.

$$lprms = \sqrt{2} \bullet lprirms \qquad (EQ. 48)$$

The current through the secondary winding is only half of the load, and its RMS currents in both transfer and freewheeling periods can be defined by EQs. 49 and 50, respectively. The overall RMS current through the secondary winding can be calculated with EQ. 51.

Isrmstr =

$$\sqrt{\left(\frac{lo^2}{4} + \frac{dl^2}{12}\right) \bullet D}$$

(EQ. 49)

Isrmsfr =

$$\sqrt{\left(\left(\frac{lo}{2} + \frac{dl}{2(2-D)}\right)^2 + \frac{dl^2(1-D)^2}{12(2-D)^2}\right) \cdot (1-D)}$$

(EQ. 50)

$$Isrms = \sqrt{Isrmstr^2 + Isrmsfr^2}$$

(EQ. 51)

The magnetizing inductance (Lmag) is determined by the number of turns of primary winding, the core geometry, and the air gap. The Lmag however should not be designed too low. If it is too low, high power dissipation will be introduced in the primary switches, and too much ramp will be added to the current ramp signal, which makes the supply look voltage mode. A reasonable small Lmag can assist ZVS and decrease any noise sensitivity problems. Around 100uH is a start point for telecom brick applications. In addition, it is recommended to have a small gap in the transformer stabilizing the magnetizing inductance so that the magnetizing current can be within a controllable range.

The leakage inductance is not an issue in the design. In fact, it is part of the commutating inductance to assist ZVS using its stored energy. Too much leakage inductance however will lower the effective duty cycle, resulting in a lower turns ratio.

The primary-to-secondary capacitance should be minimized since it robs energy from the ZVS elements increasing the resonant time and decreasing the maximum available duty cycle and the ZVS load range.

As far as the size of the transformer is concerned, it varies with applications. In the reference design, the transformer is limited to less than 0.5 inch height, being able to fit into a telecom half brick.

## **Determine Commutating Inductance**

The required external commutating inductance is determined by the slower transition (from passive to active period) since the commutating inductance stores the least energy for ZVS. The ZVS condition is that the energy stored in the commutating inductance, defined in EQ. 52, should be greater than the energy stored in the primary capacitance, defined in EQ. 53. Thus, the required external commutating inductance can be roughly estimated with EQ. 54. Refer to [1] for detailed discussion.

$$\mathsf{E}_{\mathsf{L}} = \frac{1}{2}(\mathsf{L}_{\mathsf{ext}} + \mathsf{L}_{\mathsf{k}}) \bullet (\mathsf{Imag} + \mathsf{Ip})^2 \tag{EQ. 52}$$

$$E_{C} = \frac{1}{2}(2\cos s + Cp) \bullet Vin^{2}$$

(EQ. 53)

$$L_{ext} < \frac{Vin^2 \bullet (2 \bullet Coss + Cp)}{(Imag + Ip)^2} - L_k$$

(EQ. 54)

Note that the output capacitance (Coss) of the MOSFET varies with the drain to source voltage, and the primary current (Ip) at the end of the freewheeling period determined by the turns ratio and current distribution factor  $F_{DIST}$ . The external commutating inductor however would be better defined in the real circuits by trial and errors.

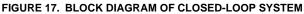

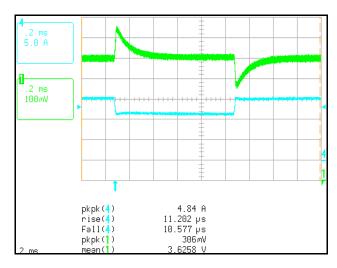

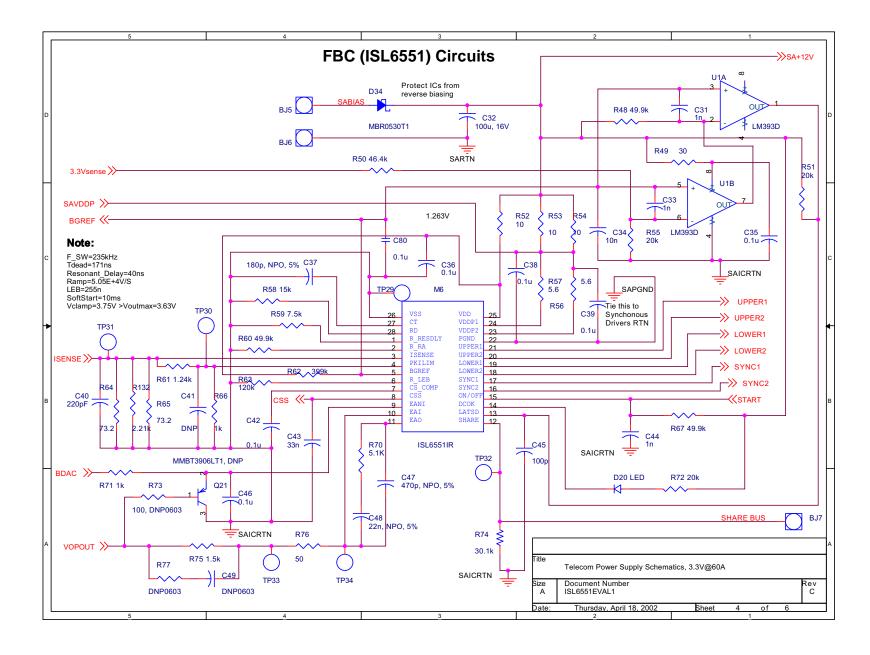

#### **Control Loop Design**

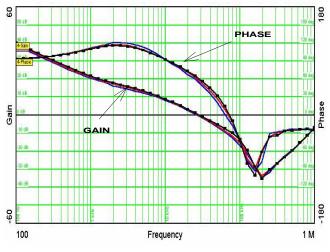

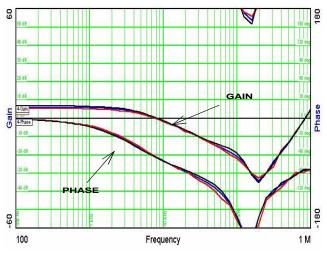

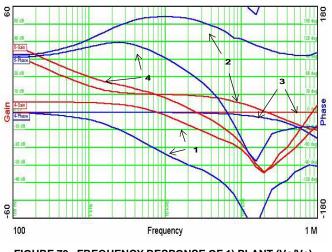

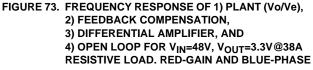

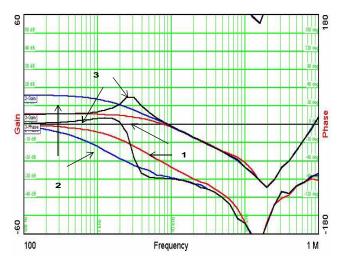

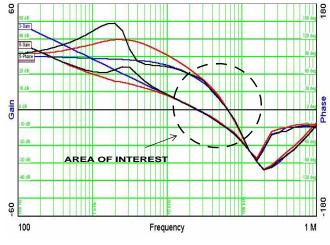

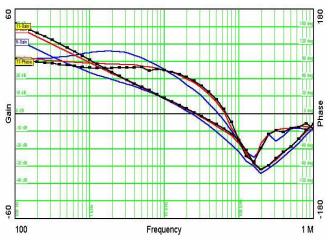

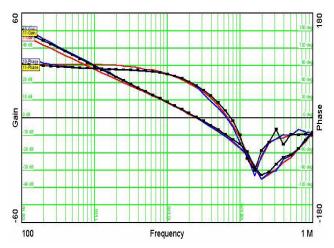

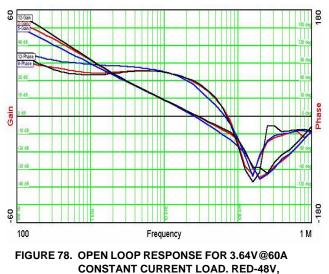

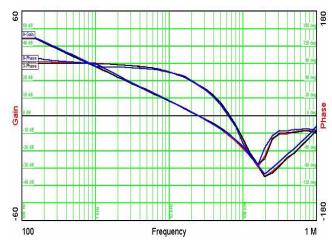

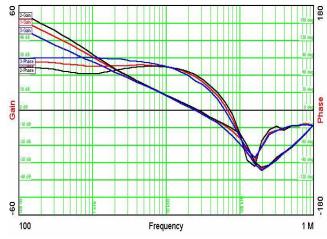

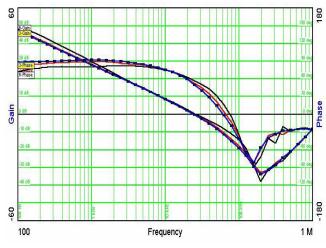

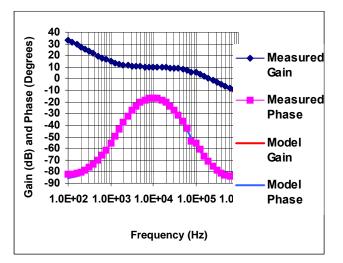

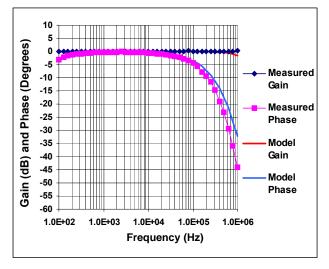

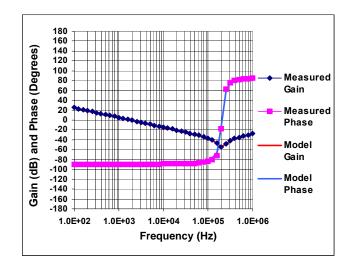

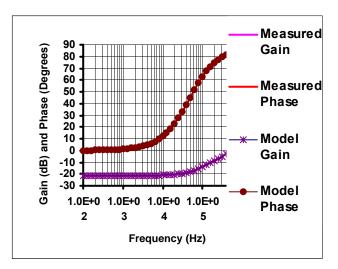

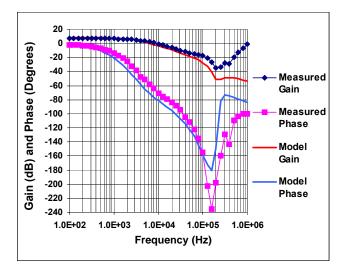

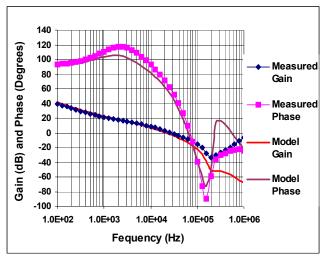

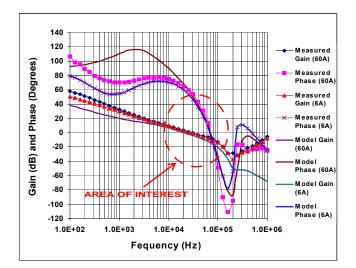

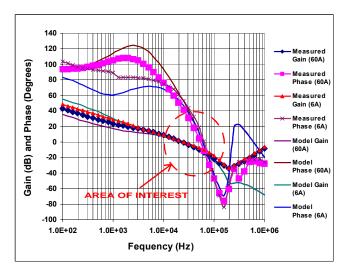

The secondary-referenced, peak current control is implemented in the converter design. Two pulse transformers pass the PWM information of the full-bridge controller (ISL6551) to two high current half-bridge drivers (HIP2100s) in the primary. A current transformer is to feed the primary current information to the full-bridge controller, as a feed-forward loop. The control loop is closed by an error amplifier, for loop compensation purpose, cascaded with a differential amplifier, for remote sense purpose. Figure 17 shows the block diagram of the overall closed-loop system.

This peak current mode controlled system can be simplified as shown in Figure 18, for setting up an initial feedback compensation, and EQ. 55 defines the approximate openloop transfer function. The factor "2" in the equation is due to that only half of the load is sensed by the current transformer.

$$Hopen(S) = \frac{2N \bullet Ncs}{Rcs} \bullet Hd(S) \bullet He(S) \bullet Zo(S)$$

(EQ. 55)

Designers should initially set a low cut-off frequency, such as 1kHz, system loop with this simplified model as a start point and then continue to modify the loop under a stable condition with a design tool such as a Venable System. Note that the model does not include the slope compensation component and does not account for subharmonic oscillation phenomenon in current-mode controlled converters. The high-frequency correction term given by EQ. 56 will account for the phenomenon [4].

$$Hs(S) = \frac{1}{1 + \frac{S}{Wn \bullet Qp} + \frac{S^{2}}{Wn^{2}}}$$

$$Wn = \pi \bullet Fsw$$

$$Qp = \frac{1}{\pi \bullet \left(Mc \bullet \left(1 - \frac{D}{2}\right) - 0.5\right)}$$

$$Mc = 1 + \frac{Se}{Sn}$$

$$Se = Sm + Sin$$

$$Sn = \frac{Vs(2 - D)}{2Lo} \bullet \frac{Rcs}{N \bullet Ncs}$$

A better representation of the open loop transfer function for the overall system is defined in EQ. 57:

$$Hopen2(S) = Hopen(S) \bullet Hs(S)$$

(EQ. 57)

Refer to Vatché's Article [3] for another way of modeling the loop.

# Special Notes for Configuring the ISL6551

The controller can be easily configured using Table 1 in the ISL6551 datasheet. In this section, several things that require the users' attention are highlighted. For a detailed configuration, please refer to the device datasheet.

- For a tighter tolerance of operating frequency, a 5% NPO ceramic capacitor is recommended for CT.

- The resonant delay should not be too long, otherwise, the residual resonant current will flow through the body diode of the lower FET and additional losses are generated. The maximum available duty cycle will also be decreased.

- The amount of slope contributed by the magnetizing current is given by EQ. 58, while the amount of slope contributed by the internal circuit of the IC is given by EQ. 59. The overall slope added to the current ramp signal is the sum of these two equations. An internal ramp (programmed by a R\_RA resistor) might not be required if the ramp contributed by the Lmag is enough for the slope compensation.

$$Sm = \frac{Vin}{Lmag} \bullet \frac{Rcs}{Ncs}$$

(EQ. 58)

$$Sin = \frac{BGREF}{R \neg RA} \bullet \frac{1}{500 \cdot 10^{-12}}$$

(EQ. 59)

• The voltage at ISENSE pin should be scaled appropriately such that the desired peak current equals or less than Vclamp-200mV-Vramp, as defined in EQ. 60. In addition, the turns ratio of the current transformer, *Ncs*, should be selected so that power losses at Rcs (current sense resistor) at the lowest line and the maximum output load is less than the power rating of one or two SMT0805 resistors so that minimum losses are induced by the Rcs and less board space is required.

$$Rcs \leq \frac{(Vclamp - 200mV) - \frac{Sin \bullet D}{Fclock}}{\frac{|pripeak}{Ncs}}$$

(EQ. 60)

- The peak current limit set by the PKILIM is lower than the cycle-by-cycle current limit controlled by the Vclamp in the reference design for two reasons: 1) ISENSE (at full load) has to be designed no greater than the minimum reference voltage (2.64V) at EANI pin, otherwise, the monotonic output startup at full load cannot be achieved; and 2) high losses can be introduced if ISENSE (at full load) is pushed up to the Vclamp (3.75V) with a low turns ratio (150:1) current transformer. In the reference design, the ISL6550 would latch the ISL6551 off in overload conditions.

- The voltage at EANI and EAO should be designed lower than the Vclamp, otherwise the output will be regulated at Vclamp and the output load will be limited to the equivalent current voltage. Since both EANI and EAO are clamped by the same voltage (Vclamp), the output voltage would dip if the current ramp exceeds the EAO during the

startup, especially for applications with constant current load. Hence, the EANI should be set higher than EAO, otherwise, the output voltage cannot have a monotonic startup. (This problem could be solved by setting the soft start at the EANI pin instead of the CSS pin allowing the clamping voltage to come up at a very high speed.) In the reference design, the synchronous FETs are turned off during start up achieving monotonic rise for resistive load applications. The FETs are turned on after a certain load and then cannot be turned off even back to no-load, which achieves a better dynamic performance. Users however can completely remove the current peak detecting circuits (D23..., they are only handy circuits for users to turned off the synchronous FETs whenever necessary) and rely on the R134 and C132 to achieve monotonicity for the output voltage startup.

- The BGREF should be kept as clean as possible, otherwise, the over current trip point set at the PKILIM would be lower than is expected due to the noise/ripple at the bandgap reference. A low ESR 0.1uF ceramic capacitor is recommended for decoupling. Due to an internal race condition, the ISL6551 cannot work properly without a 399kW resistor connecting between BGREF and VDD pins. For additional reference load (no more than 1mA), this pull-up resistor should be scaled accordingly such that the converter can start up properly. In other words, VDD should source at least the amount of BGREF external load current through the pull-up resistor.

- The SHARE pin requires a  $30k\Omega$  load. A low ESR 0.1uF or higher ceramic capacitor should be connected to the CS\_COMP pin to design a much lower current loop bandwidth than that of the voltage regulation loop in current share operation.

- It is critical that the input signal to ISENSE decays to zero prior to or during the clock dead time, otherwise, it could cause severe errors in the signal reaching the PWM comparator. Examine the current ramp tail of the converter at maximum duty cycle and full load operations, and extend the dead time to reset the current ramp tail if oscillations occur. The C61 in the peak current detecting circuits (page 6 of the schematics) causes a tail at the current ramp. If it is removed, a smaller dead time can be used while maintaining proper operations.

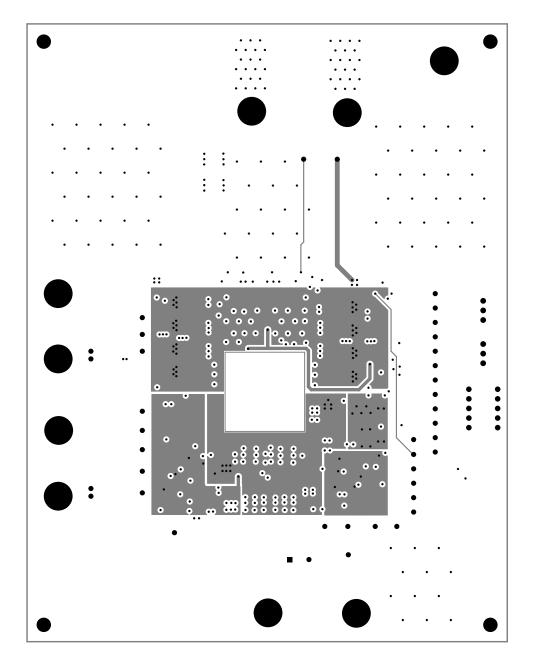

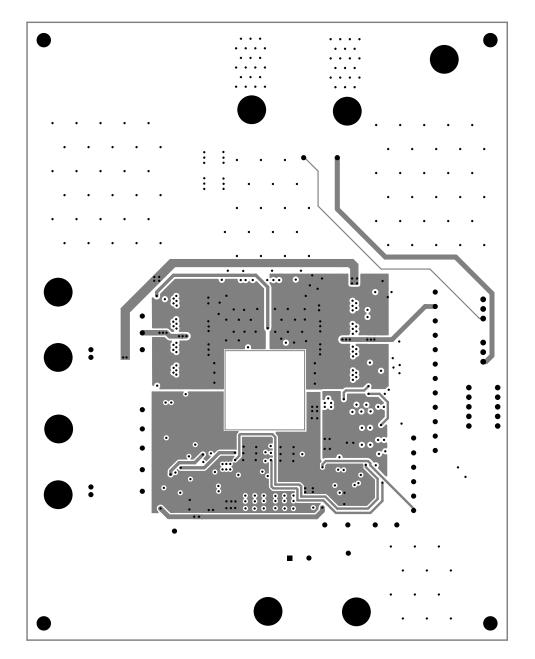

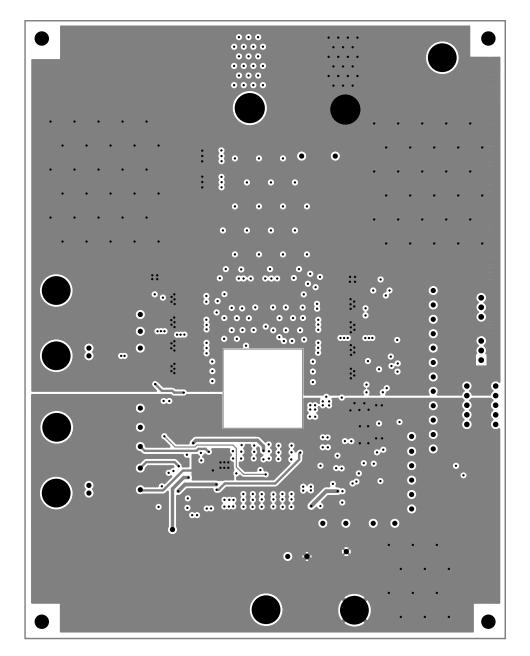

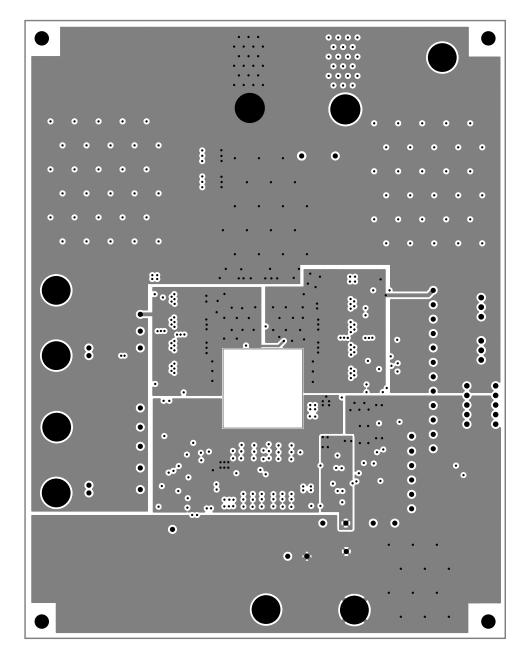

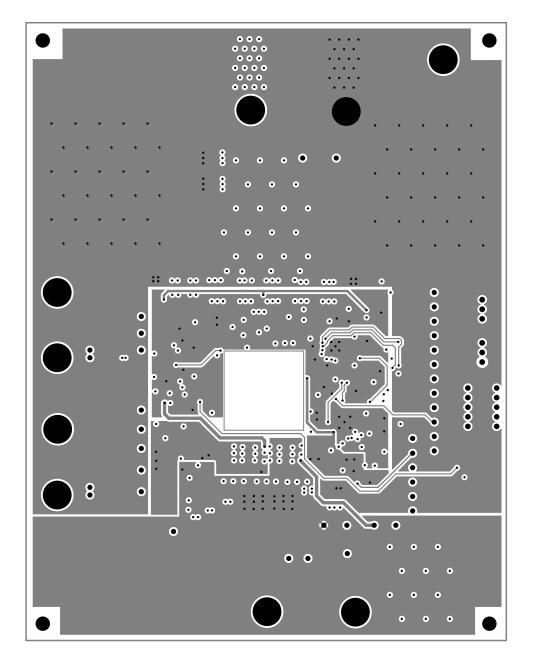

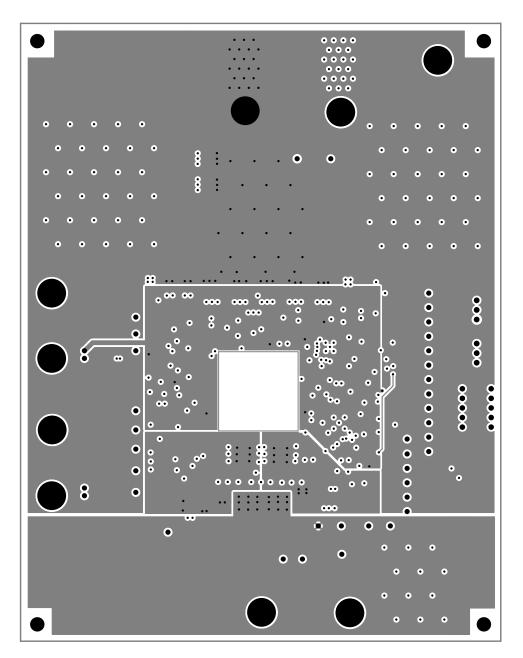

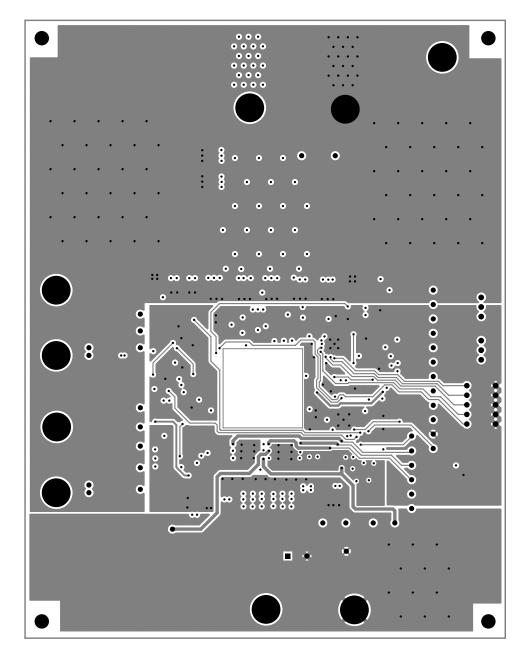

#### Layout Considerations

• When doing the layout, users should pay special attention to the VSS and PGND returns (Analog Ground and Power Ground). VSS is the reference ground, the return of VDD, of all control circuits and must be kept as clean as possible from all switching noises. It should be connected to the PGND in only one location as close to the IC as practical. For a secondary control system, it should be connected to the net after the output capacitors, i.e., the output return pinouts. For a primary control system, it should be connected to the net before the input capacitors, i.e., the input return pinouts.

- Heavy copper traces should be connected to the bias pins (VDD, VDDP1, VDDP2) and the ground pins (VSS and PGND) for heat spreading.

- The copper routings from the drivers to the FETs should be kept short and wide, especially in very high frequency applications, to reduce the inductance of the traces so that the drive signals can be kept clean, no bouncing.

- In the MLFP package, the pad underneath the center of the IC is a "floating" thermal substrate. The PCB "thermal

land" design for this exposed die pad should include thermal vias that drop down and connect to buried copper plane(s). This combination of vias for vertical heat escape and buried planes for heat spreading allows the MLFP to achieve its full thermal potential. It is recommended to connect this pad to the low noise copper plane Vss.

• For additional tips, please refer to "PCB Design Guidelines For Reduced EMI" [5].

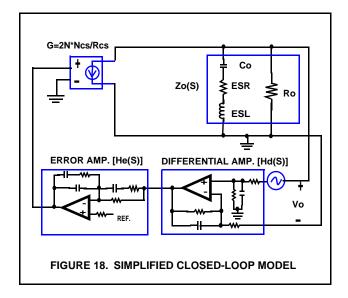

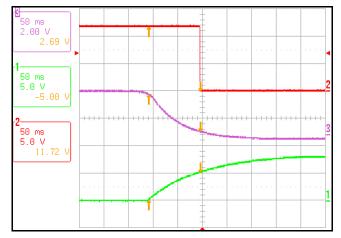

FIGURE 19. SHUTDOWN TIMING DIAGRAM OF THE CONVERTER

## Shutdown Timing Diagram of the Converter

**INPUT UV (1):** With all the biases powered up and the mechanical switch at the PEN pin turned on, the converter is enabled after the input reaches its turn-on threshold (34.3V). The output voltage rises to its regulation point following the soft start. The soft start capacitor continues to be charged up to the clamping voltage (Vclamp). The DCOK is pulled low indicating "GOOD" once the output reaches within -3% of the set point.

**ENABLE (2):** When the PEN pin is pulled low, the soft start capacitor is discharged very quickly and all the drivers are disabled. The DCOK is pulled high indicating "FAULT" when

the output voltage is discharged below -5% of the set point. When the PEN pin is released, a soft start is initiated.

**OVER CURRENT (3):** If the output of the converter is over loaded, i.e, the PKILIM is above the bandgap reference (BGREF), the soft start capacitor is discharged quickly and all the drivers are turned off. Once the output voltage is below -8.33% of the regulation point, the capacitor of the under-voltage delay set at ISL6550 is then charged up, and the START is latched when the voltage at the capacitor reaches 5V. The ISL6551 controller is quickly shut down by the START. If the over load is removed and the converter can return to normal operation within the under-voltage delay (around 70mS), then the START will not be latched. The latch can be reset by the PEN signal, which is controlled by the input voltage, the mechanical switch, and the thermal condition of the converter. If latching the converter off in overload conditions is not allowed, then version B of ISL6550 can be used. Then the converter would be running in hiccup mode in overload conditions.

**OUPUT UV & LOCAL OV (4):** If the output voltage is beyond +/-8.33% of the set point and does not reach the master OV setpoint (4.19V) for any reason, the START is then latched, so is the converter. The latch can be reset by the PEN.

**OUPTUT MASTER OV (5):** If the master OV circuit is triggered, the LATSD is pulled high and latches the controller off. The latch can be reset ONLY by cycling VDD. It CANNOT be reset by toggling ENABLE (PEN).

**RESET LATCH (6):** The soft start capacitor starts to be charged after the VDD increases above the ISL6551 and ISL6550 turn-on thresholds.

**VDD UV LOCKOUT (7):** The IC is turned off when the VDD is below the ISL6551 and ISL6550 turn-off thresholds. The soft start is reset.

**INPUT UV LOCKOUT (8):** When the input voltage is below its turn-off threshold 33.3V, the converter is disabled and latched off. The soft start is reset.

#### Summary of Design

Table 1 is the BDAC output programming code.

| TABLE 1. BDAC OUTPUT PROGRAMMING CODE |

|---------------------------------------|

|---------------------------------------|

| #  | VID4 | VID3 | VID2 | VID1 | VID0 | V <sub>OUT</sub> (V) |

|----|------|------|------|------|------|----------------------|

| 0  | 1    | 1    | 1    | 1    | 1    | 2.642                |

| 1  | 1    | 1    | 1    | 1    | 0    | 2.674                |

| 2  | 1    | 1    | 1    | 0    | 1    | 2.706                |

| 3  | 1    | 1    | 1    | 0    | 0    | 2.738                |

| 4  | 1    | 1    | 0    | 1    | 1    | 2.770                |

| 5  | 1    | 1    | 0    | 1    | 0    | 2.801                |

| 6  | 1    | 1    | 0    | 0    | 1    | 2.833                |

| 7  | 1    | 1    | 0    | 0    | 0    | 2.865                |

| 8  | 1    | 0    | 1    | 1    | 1    | 2.897                |

| 9  | 1    | 0    | 1    | 1    | 0    | 2.929                |

| 10 | 1    | 0    | 1    | 0    | 1    | 2.961                |

| 11 | 1    | 0    | 1    | 0    | 0    | 2.993                |

| 12 | 1    | 0    | 0    | 1    | 1    | 3.025                |

| 13 | 1    | 0    | 0    | 1    | 0    | 3.057                |

| 14 | 1    | 0    | 0    | 0    | 1    | 3.089                |

| 15 | 1    | 0    | 0    | 0    | 0    | 3.121                |

| 16 | 0    | 1    | 1    | 1    | 1    | 3.153                |

#### TABLE 1. BDAC OUTPUT PROGRAMMING CODE

| TABLE I. BDAC OUTFUT FROGRAMMING CODE |      |      |      |      |      |                      |

|---------------------------------------|------|------|------|------|------|----------------------|

| #                                     | VID4 | VID3 | VID2 | VID1 | VID0 | V <sub>OUT</sub> (V) |

| 17                                    | 0    | 1    | 1    | 1    | 0    | 3.185                |

| 18                                    | 0    | 1    | 1    | 0    | 1    | 3.216                |

| 19                                    | 0    | 1    | 1    | 0    | 0    | 3.248                |

| 20                                    | 0    | 1    | 0    | 1    | 1    | 3.280                |

| 21                                    | 0    | 1    | 0    | 1    | 0    | 3.312                |

| 22                                    | 0    | 1    | 0    | 0    | 1    | 3.344                |

| 23                                    | 0    | 1    | 0    | 0    | 0    | 3.376                |

| 24                                    | 0    | 0    | 1    | 1    | 1    | 3.408                |

| 25                                    | 0    | 0    | 1    | 1    | 0    | 3.440                |

| 26                                    | 0    | 0    | 1    | 0    | 1    | 3.472                |

| 27                                    | 0    | 0    | 1    | 0    | 0    | 3.504                |

| 28                                    | 0    | 0    | 0    | 1    | 1    | 3.536                |

| 29                                    | 0    | 0    | 0    | 1    | 0    | 3.568                |

| 30                                    | 0    | 0    | 0    | 0    | 1    | 3.599                |

| 31                                    | 0    | 0    | 0    | 0    | 0    | 3.631                |

Table 2 summarizes major design parameter requirements. Most components are selected or designed based on these values. Users should generate a similar table for their applications and select components with derating guideline of the datasheet or their own companies.

#### TABLE 2. DESIGN PARAMETER REQUIREMENTS

| PARAMETER                          | CONDITION                                                                                            |      | UNIT |  |  |

|------------------------------------|------------------------------------------------------------------------------------------------------|------|------|--|--|

| DUTY CYCLE AND SWITCHING FREQUENCY |                                                                                                      |      |      |  |  |

| Dmaxav                             | t <sub>DEAD</sub> =200ns, t <sub>RESDLY</sub> =100ns,<br>Fsw=250kHz                                  |      | %    |  |  |

| Fsw                                | CT=180pF                                                                                             | 235  | kHz  |  |  |

|                                    | INPUT CAPACITORS                                                                                     |      |      |  |  |

| Cin                                | D=0.5, dVincap=1.65V                                                                                 | 3    | uF   |  |  |

| linrms                             | Vin=48V, D~0.5, Vo=3.63V                                                                             | 5.4  | А    |  |  |

|                                    | OUTPUT CAPACITORS                                                                                    |      |      |  |  |

| Со                                 | f <sub>c</sub> =Fsw/10=23.5kHz                                                                       | 677  | uF   |  |  |

| dlo                                | dlo Lo=0.8uH, Vin=75V, Vo=3.63V                                                                      |      | А    |  |  |

| lorms                              | lorms Vin=75V, Lo=8uH, Vo=3.63V                                                                      |      | А    |  |  |

| ESR                                | dVtr = 150mV @ 25% Load Step                                                                         | 10   | mΩ   |  |  |

|                                    | OUTPUT INDUCTORS                                                                                     | •    |      |  |  |

| dl                                 | Lo=0.8uH, Vin=75V, Vo=3.63V                                                                          | 16.3 | А    |  |  |

| lindpeak                           | Io=60A, Vin=75V, Vo=3.63V<br>assuming the load evenly distributed<br>between both output inductors   | 38.2 | A    |  |  |

| lindrms                            | s Io=60A, Vin=75V, Vo=3.63V<br>assuming the load evenly distributed<br>between both output inductors |      | A    |  |  |

19

## TABLE 2. DESIGN PARAMETER REQUIREMENTS (Continued)

| PARAMETER                                                                                                        | CONDITION                                                                                                   | VALUE | UNIT |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------|------|

|                                                                                                                  | MAIN TRANSFORMER                                                                                            |       | 1    |

| Imag                                                                                                             | Lmag=60uH (Limited by Core),<br>Vo=3.63V, Fsw                                                               |       | A    |

| Ipripeak                                                                                                         | Vin=75V, Vo=3.63V                                                                                           | 11.4  | Α    |

| Iprms                                                                                                            | VIN=75V, Vo=3.63V                                                                                           | 9.9   | А    |

| Isrms                                                                                                            | Vin=75V, Vo=3.63V                                                                                           | 33.4  | А    |

| Ν                                                                                                                | Limited by Core                                                                                             | 7:2   | -    |

| Nmax                                                                                                             | Vin=36V, Vomax=3.63V,<br>Vmisc=0.3V, Dmaxav=0.85                                                            | 3.77  | -    |

|                                                                                                                  | CURRENT TRANSFORMER                                                                                         |       |      |

| Ncs                                                                                                              |                                                                                                             | 150:1 | -    |

|                                                                                                                  | PRIMARY SWITCHES                                                                                            |       |      |

| Ipriavgfr                                                                                                        | Vin=75V, Vo=3.63V                                                                                           | 3.6   | А    |

| Ipriavgres                                                                                                       | Ipriavgres Vin=36V, Vo=3.63V                                                                                |       | А    |

| Iprirms                                                                                                          | Vin=75V, Vo=3.63V                                                                                           | 4.94  | А    |

| lprirsmtr                                                                                                        | Vin=75V, Vo=3.63V                                                                                           | 2.57  | А    |

| lprirsmtr                                                                                                        | Vin=36V, Vo=3.63V                                                                                           | 3.71  | А    |

| Pdr Each Primary Driver<br>Vcc(max)=13.2, Qg=50nC x 2 at<br>V <sub>GS</sub> =10V, Two Siliconix SUD40N10-<br>25  |                                                                                                             | 0.42  | W    |

| Pupfet                                                                                                           | Vin=75V, Vd=0.78V, Vo=3.63V                                                                                 | 4.1   | W    |

| Plowfet Vin=36V, Vd=0.75V, Vo=3.63V with<br>Td=40n. The worse case could be at<br>Vin=75 due to switching losses |                                                                                                             | 0.90  | W    |

|                                                                                                                  | SYNCHRONOUS FETs                                                                                            |       |      |

| lsynpeak                                                                                                         | Vin=75V, Vo=3.63V                                                                                           | 66.4  | А    |

| Isynrms                                                                                                          | Vin=75V, Vo=3.63V                                                                                           | 42.5  | А    |

| Pdr                                                                                                              | Each Secondary Driver<br>Vcc(max)=13.2V, Qg=30nC x 4 at<br>V <sub>GS</sub> =4.5V<br>Four Siliconix Si4842DY | 1.09  | W    |

| Psynfet                                                                                                          | Vin=75V, Four Siliconix Si4842DYs.<br>Body Diode Conduction and<br>Recovery Losses are not Included<br>Here | 2.3   | W    |

Table 3 summarizes a rough full load power losses analysis for 3.3V output of the reference design.

#### TABLE 3. FULL LOAD POWER LOSSES ANALYSIS

| TABLE 3. FULL LOAI                                                                                                                                                                    | POWER DISSIPATION<br>AT 60A LOAD |                         |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------|--------|

| ELEMENTS                                                                                                                                                                              | 36V                              | 48V                     | 75V    |

| CALCULA                                                                                                                                                                               | ITIONS                           |                         |        |

| Clock Dead Time                                                                                                                                                                       |                                  | 175ns                   |        |

| Resonant Time                                                                                                                                                                         |                                  | 50ns                    |        |

| Td                                                                                                                                                                                    |                                  | 40ns                    |        |

| Switching Frequency                                                                                                                                                                   |                                  | 235kHz                  |        |

| Transformer Turns Ratio                                                                                                                                                               |                                  | 7:2                     |        |

| Magnetizing Inductance                                                                                                                                                                |                                  | 60uH                    |        |

| Output Inductor                                                                                                                                                                       |                                  | 0.8uH                   |        |

| MOSFET Rds(on) Value                                                                                                                                                                  |                                  | at Tj=50 <sup>0</sup> C |        |

| PRI                                                                                                                                                                                   | MARY SIDE                        |                         |        |

| Upper FETs Conduction                                                                                                                                                                 | 2.616W                           | 3.371W                  | 4.179W |

| Lower FETs Conduction                                                                                                                                                                 | 0.819w                           | 0.630W                  | 0.427W |

| Primary Winding Copper                                                                                                                                                                | 1.023W                           | 1.087W                  | 1.155W |

| Current Sense Winding                                                                                                                                                                 | 0.110W                           | 0.082W                  | 0.053W |

| Pinouts of Current Sense<br>Transformer                                                                                                                                               | 1.521W                           | 1.141W                  | 0.731W |

| Full Bridge Drivers                                                                                                                                                                   | 0.677W                           | 0.677W                  | 0.677W |

| SECONDARY SIDE                                                                                                                                                                        |                                  |                         |        |

| Synchronous FETs<br>Conduction                                                                                                                                                        | 2.290W                           | 2.293W                  | 2.296W |

| Secondary Winding Copper                                                                                                                                                              | 1.005W                           | 1.054W                  | 1.106W |

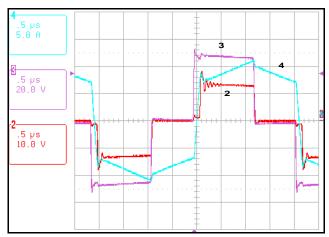

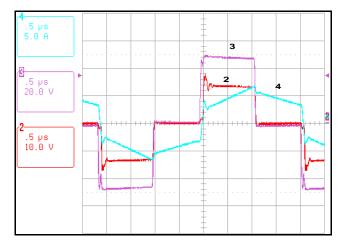

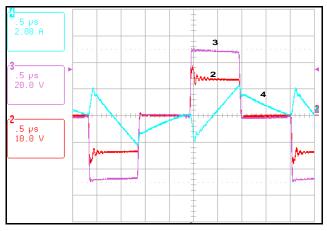

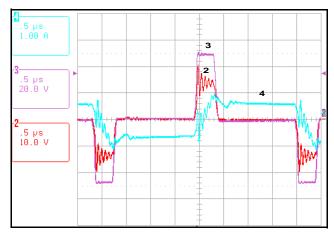

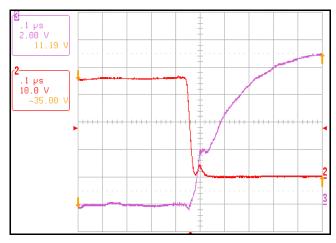

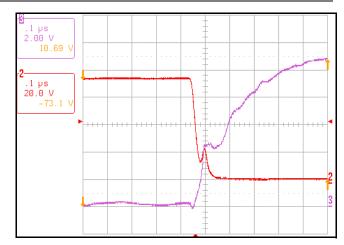

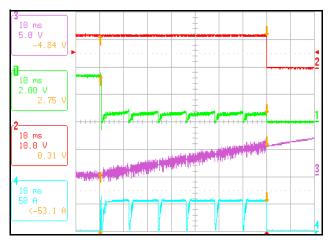

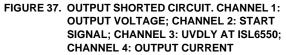

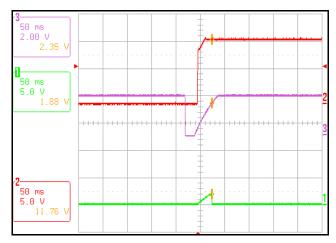

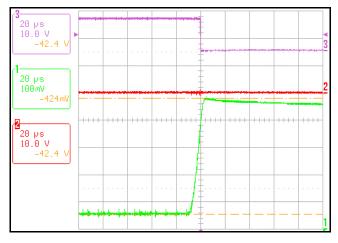

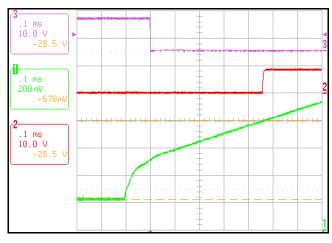

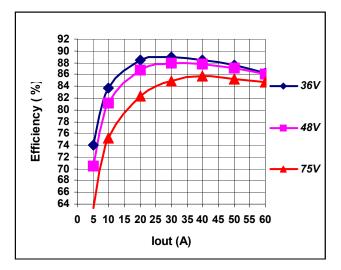

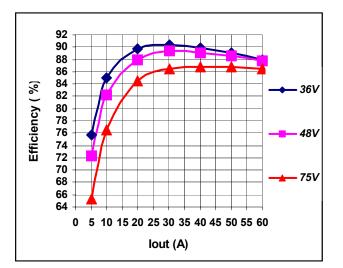

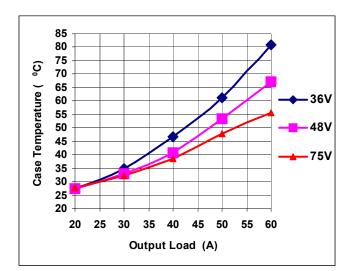

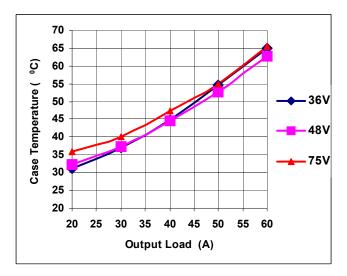

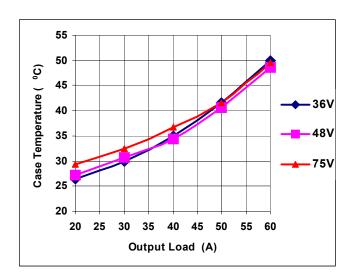

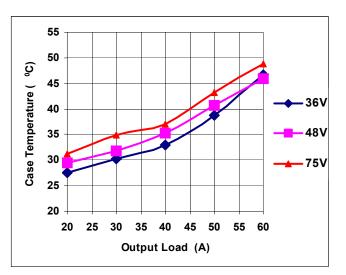

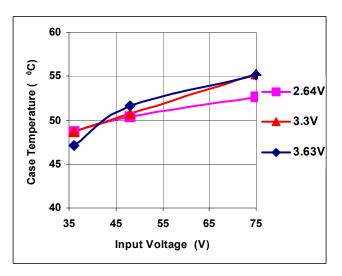

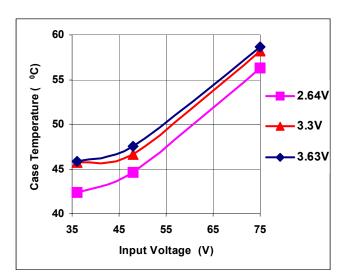

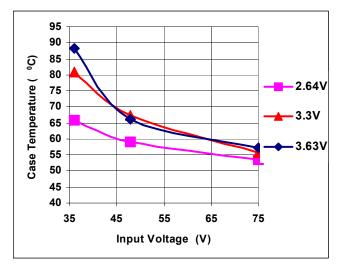

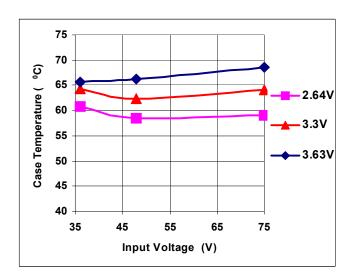

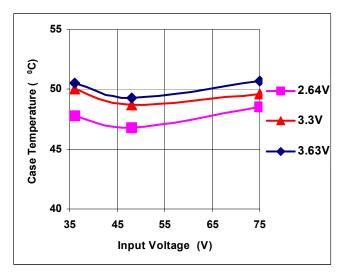

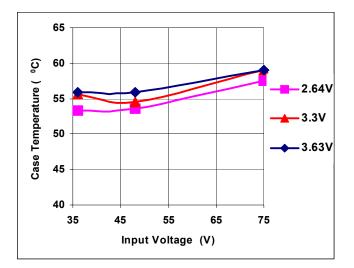

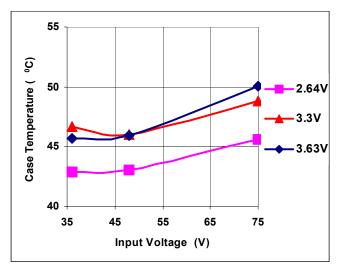

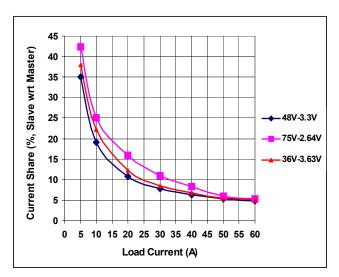

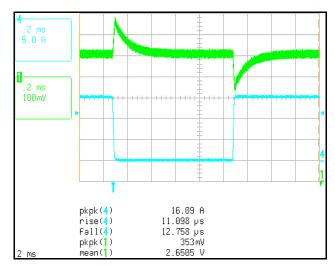

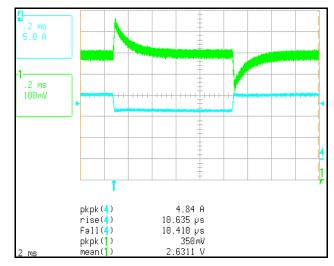

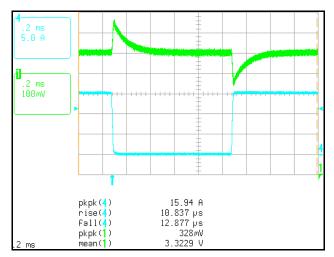

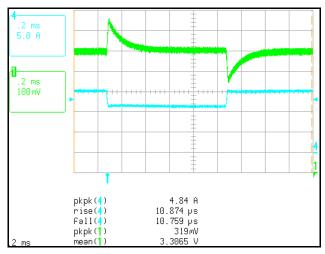

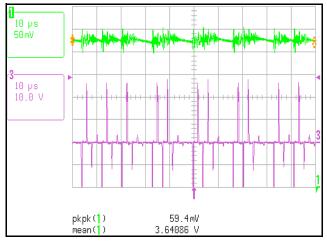

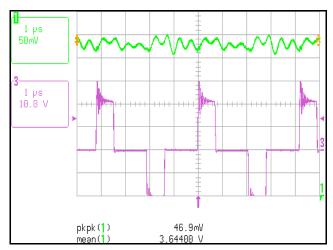

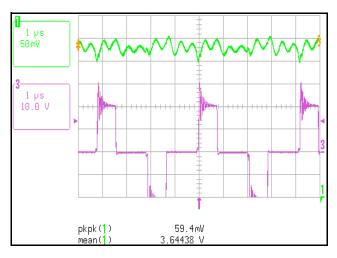

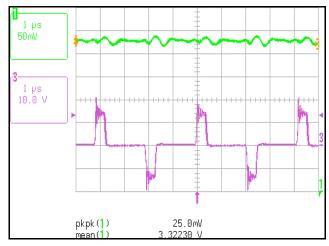

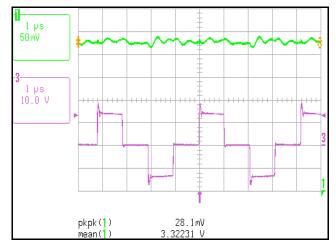

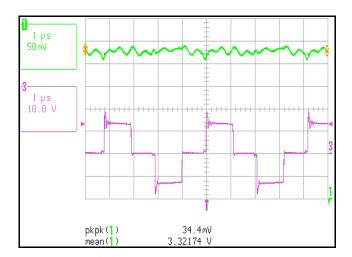

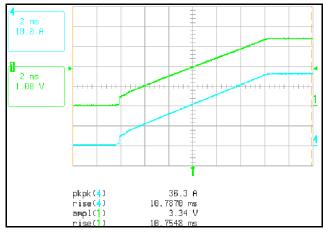

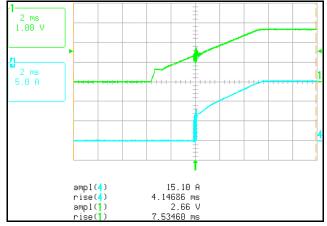

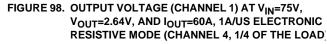

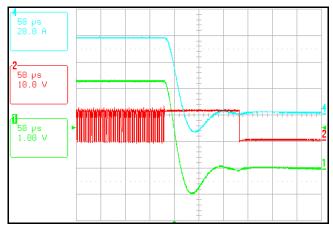

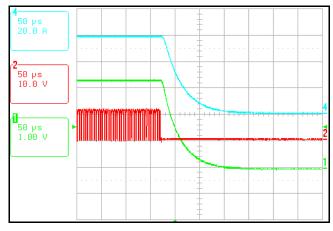

| Output Inductors Copper                                                                                                                                                               | 2.575W                           | 2.642W                  | 2.716W |